学校代码: 10246

学 号: 10210720162

# 復旦大學

# 硕士学位论文

# 宽带分数分频频率综合器中电荷 泵和分频器电路设计

院 系: 信息科学与工程学院

专业: 集成电路工程

姓名:万熊熊指导教师:唐长文

完成日期: 2012年04月30日

# 目 录

| 图目录   | ₹•••• |                               | · III |

|-------|-------|-------------------------------|-------|

| 表目录   | ₹     |                               | VII   |

|       |       |                               |       |

| Abstr |       |                               |       |

| 第一章   |       | 绪论                            |       |

| -     |       | 研究背景                          |       |

| 1.    |       | 论文的主要贡献                       |       |

| 1.    | .3    | 论文的研究内容和组织结构                  | 2     |

| 第二章   | 章 🤌   | 频率综合器概述                       | 5     |

| 2     | .1    | 引言                            | 5     |

| 2     | .2    | 频率综合器                         | . 5   |

| 2     | .3    | 重要参数                          | 7     |

|       | 2     | 2.3.1 相位噪声                    | 7     |

|       | 2     | 2.3.2 毛刺                      | 10    |

|       | 2     | 2.3.3 锁定时间                    | 12    |

| 2.    | .4    | 设计流程                          | 13    |

| 2     | .5    | 本章小结                          | 14    |

| 第三章   | 章 !   | 鉴频鉴相器分析与设计                    | 15    |

| 3.    | .1    | 引言                            | 15    |

|       |       | PFD/CP·····                   |       |

| 3.    | .3    | 设计考虑                          | 17    |

|       | ;     | 3.3.1 非理想效应                   | 17    |

|       | (     | 3.3.2 PFD/CP 的相位噪声 ·······    | 19    |

|       | ;     | 3.3.3 非线性考虑                   | 20    |

|       | (     | 3.3.4 导通时间                    | 22    |

| 3.    | .4    | 鉴频鉴相器电路设计                     | 23    |

|       | ;     | 3.4.1 降低非线性技术                 | 23    |

|       | ;     | 3.4.2 鉴频鉴相器电路                 | 25    |

|       | ;     | 3.4.3 Lock Detector 电路······· | 26    |

|       | (     | 3.4.4 鉴频鉴相器版图                 | 26    |

|       | ;     | 3.4.5 工作模式                    | 27    |

| 3.    | .5    | 本章小结                          | 27    |

| 第四章   | 至     | 全差分电荷泵分析与设计                   | 29    |

| 4.1     | 引言…   |                                              | 29    |

|---------|-------|----------------------------------------------|-------|

| 4.2     | 全差分   | <b>}</b> 电荷泵                                 | ·· 29 |

| 4.3     | 设计考   | <b>挎虑</b>                                    | ·· 31 |

|         | 4.3.1 | 晶体管尺寸的选择 ······                              | ·· 31 |

|         | 4.3.2 | 非理想因素及解决方案                                   | 32    |

|         | 4.3.3 | 管子间 mismatch 的影响······                       | 33    |

|         | 4.3.4 | 电荷泵电流的影响                                     | 35    |

| 4.4     | 电荷泵   | ē电路设计                                        | 36    |

|         | 4.4.1 | 全差分电路 · · · · · · · · · · · · · · · · · · ·  | 36    |

|         | 4.4.2 | CMFB 电路······                                | 37    |

|         | 4.4.3 | 电荷泵版图                                        | 38    |

|         | 4.4.4 | 仿真结果                                         | 39    |

| 4.5     | 本章小   | 、结                                           | ·· 41 |

| 第五章     | 分频器   | 8分析与设计                                       | 43    |

| 5.1     | 引言…   |                                              | ·· 43 |

| 5.2     | 分频器   | <b>8</b> 设计                                  | ·· 43 |

|         | 5.2.1 | 4/5 预分频器 ······                              | . 44  |

|         | 5.2.2 | 时序问题                                         | ·· 46 |

|         | 5.2.3 | 4/5 预分频器电路设计                                 | ·· 47 |

|         | 5.2.4 | 4/5 预分频器版图                                   | ·· 49 |

|         | 5.2.5 | 仿真结果                                         | ·· 49 |

| 5.3     | 正交分   | · 频器设计 · · · · · · · · · · · · · · · · · · · | 51    |

|         | 5.3.1 | I/Q 失配的影响 ······                             | 51    |

|         | 5.3.2 | I/Q 分频器结构 ······                             | 53    |

|         | 5.3.3 | 二分频器电路                                       | 54    |

|         | 5.3.4 | I/Q 分频器版图 ······                             | 59    |

|         | 5.3.5 | 仿真结果                                         | 60    |

| 5.4     | 本章小   | 、结                                           | 60    |

| 第六章     | 总结与   | <b>5展望</b>                                   | 61    |

| 6.1     | 工作总   | 9.结······                                    | ·· 61 |

| 6.2     | 未来展   | ē望······                                     | ·· 61 |

| 参考文献    | ŧ     |                                              | 64    |

| <b></b> |       |                                              | 68    |

# 图目录

| 图 1-1  | ΔΣ 分数分频频率综合器                                                  | 1  |

|--------|---------------------------------------------------------------|----|

| 图 2-1  | 整数分频频率综合器                                                     |    |

| 图 2-2  | 分数分频频率综合器 ······                                              | 6  |

| 图 2-3  | $\Delta \Sigma$ 调制器对噪声的整形···································· | 7  |

| 图 2-4  | 相位噪声的影响                                                       | 8  |

| 图 2-5  | 相位噪声                                                          | 8  |

| 图 2-6  | 整数分频频率综合器的 s 域模型                                              | 8  |

| 图 2-7  | 整数分频频率综合器相位噪声模型                                               | 9  |

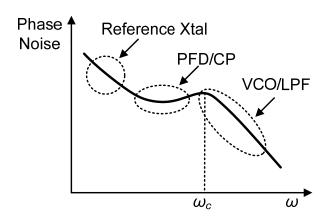

| 图 2-8  | 频率综合器各模块的噪声分布                                                 | 10 |

| 图 2-9  | 输出频谱与波形的抖动                                                    | 11 |

| 图 2-10 | 输出频率的瞬态响应                                                     | 12 |

| 图 2-11 | PLL Design Kit ·····                                          |    |

| 图 2-12 | 频率综合器设计流程                                                     | 14 |

| 图 3-1  | 异或门型和触发器型鉴相器                                                  | 15 |

| 图 3-2  | 电荷泵型鉴频鉴相器 PFD/CP······                                        |    |

| 图 3-3  | PFD/CP 工作过程 ·······                                           |    |

| 图 3-4  | PFD/CP 的死区效应 · · · · · · · · · · · · · · · · · · ·            |    |

| 图 3-5  | 死区效应的消除方法                                                     |    |

| 图 3-6  | 鉴频鉴相器上下开关的延时差异                                                |    |

| 图 3-7  | 延迟平衡的差分输出鉴频鉴相器                                                |    |

| 图 3-8  | PFD/CP 的非线性 ······                                            |    |

| 图 3-9  | PFD/CP 输入输出的时序波形······                                        |    |

| 图 3-10 | 不同导通时间下的电流噪声仿真结果                                              | 23 |

| 图 3-11 | 添加直流偏置电流源电路                                                   |    |

|        | PFD/CP 的线性化······                                             |    |

| 图 3-13 | PFD 具体电路······                                                |    |

| 图 3-14 |                                                               |    |

| 图 3-15 |                                                               |    |

| 图 3-16 | PFD 版图······                                                  |    |

| 图 4-1  | 全差分电荷泵的框架图                                                    |    |

|        | 三阶无源滤波器及其开环环路的波特图                                             |    |

|        | 单端输出电荷泵及开关电容模型                                                |    |

| 图 4-4  | 单端输出电荷泵及开关电容模型                                                | 33 |

| 图 4-5  | 晶体管阈值电压的随机不匹配                                     | 34 |

|--------|---------------------------------------------------|----|

| 图 4-6  | 全差分电荷泵支路电流源的不匹配                                   | 35 |

| 图 4-7  | 全差分电荷泵电路                                          | 37 |

| 图 4-8  | 共模反馈电路                                            | 37 |

| 图 4-10 | CMFB 电路的瞬态特性 ·······                              | 38 |

| 图 4-11 | 电荷泵版图                                             | 39 |

| 图 4-9  | 电荷泵直流匹配特性                                         | 39 |

| 图 4-12 | 电荷泵动态匹配性能                                         | 40 |

| 图 4-13 | 电荷泵 <b>qp</b> 特性                                  | 40 |

| 图 4-14 | 电荷泵 qp 曲线斜率 · · · · · · · · · · · · · · · · · · · | 41 |

| 图 5-1  | ΔΣ 调制器控制的分数分频器                                    | 43 |

| 图 5-2  | 同步 4/5 预分频器                                       | 44 |

| 图 5-3  | 4/5 预分频工作在 4 分频模式                                 | 45 |

| 图 5-4  | 4/5 预分频工作在 5 分频模式                                 | 45 |

| 图 5-5  | 4/5 预分频的状态图                                       | 45 |

| 图 5-6  | 4/5 预分频中的延时问题                                     | 46 |

| 图 5-7  | 4/5 预分频对 mod 信号的延时要求 ······                       | 46 |

| 图 5-8  | CML 结构的 D 触发器······                               | 47 |

| 图 5-9  | 集成与非门的 CML 锁存器结构                                  | 47 |

| 图 5-10 | 4/5 预分频器的实际电路                                     |    |

| 图 5-11 | 差分转单端电路                                           | 48 |

| 图 5-12 | 4/5 预分频器版图                                        | 49 |

| 图 5-13 | 5 分频仿真结果                                          | 50 |

| 图 5-14 | 4 分频仿真结果                                          | 50 |

| 图 5-15 |                                                   |    |

| 图 5-16 | 正交零中频混频                                           | 52 |

| 图 5-17 | I/Q 失配对解调后的数字信号的影响                                | 52 |

| 图 5-18 | I/Q 分频器基本框架图                                      |    |

| 图 5-19 | 改进的 I/Q 分频器框架图                                    | 53 |

| 图 5-21 | 缓冲器电路/开关电路                                        | 54 |

| 图 5-22 | CML 结构的二分频电路······                                | 55 |

| 图 5-23 |                                                   |    |

| 图 5-24 | 灵敏度仿真曲线                                           | 57 |

| 图 5-25 |                                                   |    |

| 图 5-26 | 二分频器版图                                            | 58 |

| 图 5-27 | I/Q 分频器版图 ····································    | 59 |

# 表目录

| 表 3-1 | 鉴频鉴相器的工作模式         | 27 |

|-------|--------------------|----|

| 表 5-1 | I/Q 分频器后仿结果 ······ | 60 |

# 摘要

本论文围绕 ΔΣ 分数分频频率综合器的设计展开,主要包括鉴频鉴相器、电荷泵、分频器以及 I/Q 分频器等电路模块的设计。该频率综合器应用于一款 CMOS 全集成直接变频结构的数字电视调谐器芯片。为了把 VHF/UHF 频段上的数字电视信号下变频到零中频,需要其提供 48~869MHz 的正交本振信号。因此,该频率综合器对频率范围及信噪比有着较高要求,这也给电路的设计带来了诸多挑战。

首先,论文对频率综合器做了概述,介绍了基于锁相环的分数分频频率综合器的几个关键性能指标,并且总结了频率综合器的设计流程。这对具体电路的设计具有指导意义。

其次,论文详细讨论了频率综合器中几个模块的设计。针对电荷泵型鉴频鉴相器的非线性特性,本文提出了一种降低非线性的技术,来减小鉴频鉴相器和电荷泵对带内噪声的贡献。针对全差分电荷泵复杂的电路结构,本文采用源端开关型电荷泵单元,从而简化了电路,并且使得电荷泵上下电流的调节来得更为简单。在 I/Q 分频器的设计中,本文采用 CML 结构的除二分频器来满足电路对正交匹配特性的较高要求,并且通过引入一个对输入信号放大整形的电路,很好地解决了困扰电路的灵敏度问题。

最后,给出了相应电路模块的版图以及仿真结果,验证了电路功能的正确性。本文参与设计的频率综合器在 TSMC 的 0.18μm 的工艺下成功流片,频率范围覆盖 0.8GHz~1.8GHz,总的芯片面积为 0.9mm×0.9mm。其中鉴频鉴相器和电荷泵的功耗为 1.4mA,4/5 预分频器的功耗为 1.2mA,I/Q 分频器的功耗为 4~6mA。环路滤波器的带宽为 75kHz。I/Q 分频器的正交相位误差小于 0.5°。带内相位噪声低于-100dBc/Hz。锁定时间小于 30μs。

**关键词:** 电视接收机,频率综合器,鉴频鉴相器,全差分电荷泵,线性化技术, I/Q 分频器,4/5 预分频器,相位噪声

中文分类号: TN4

# **Abstract**

This thesis takes efforts on the design of a  $\Delta\Sigma$  fractional frequency synthesizer, including phase detector, charge pump, divider and I/Q divider blocks. Applied to a CMOS fully integrated conversion structure of the digital TV tuner, the frequency synthesizer should generate a quadrature local oscillator signal ranging from 48MHz to 869MHz, which used to the conversion of the UHF/VHF band frequency to zero IF. Inevitably, some challenges are invited for high requirements, such as the wide frequency range, the high SNR, etc.

Firstly, this thesis presents a review of the frequency synthesizer, which of described three main fundamental figures of merit, and it concludes the process of the frequency synthesizer design. All over the work will be instructive.

Secondly, this thesis is mainly dedicated to the analysis and the design of four modules: phase detector, charge pump, divider and I/Q divider circuits. In terms of PFD/CP nonlinearity, a linearization technology was proposed to alleviate the contribution of PFD phase noise inband; In terms of the complexity of the fully differential charge pump, the core unit of charge pump is redesigned for simplification, also with regulating current mismatch easier; In terms of high requirement on the quadrature characteristic, circuits and layout work are coordinated to optimize the design; And also, a variation on the structure of I/Q divider was adopted, taking into account the sensitivity and the power requirements.

Finally, thanks to the other colleagues' work, including voltage controlled oscillator, loop controlled blocks etc., a 0.8GHz~1.8GHz  $\Delta\Sigma$  fractional frequency synthesizer was implemented in TSMC 0.18- $\mu$ m process successfully. The chip area is 0.81mm²; and the PFD/CP power is 1.4mA, the 4/5 prescaler power is 1.5mA, the I/Q divider power changed along with frequency and divided ratio is about 4~6mA; the inband noise is below -100dBc/Hz; the bandwith of loop fliter is 75kHz; the quadrature phase error is under 0.5°; the locking time is less than 30 $\mu$ s.

**Key Words:** Television Receiver; Frequency Synthesizer; Phase Frequency Detector; A Fully Differential Charge Pump; Linearization Technique; I/Q Divider; 4/5 Prescaler; Phase Noise

# 第一章 绪论

## 1.1 研究背景

随着无线通讯技术的迅猛发展,基于移动终端的多媒体也得到了广泛的应用。在数字电视广播领域,由于标准协议的制定,会带来高额的专利费并且主导整个领域的游戏规则。鉴于数字广播的重要性,世界上许多国家都积极制定了各自的数字电视广播标准,如中国自主研发的CMMB(China Mobile Multimedia Broadcasting)标准,欧洲的DVB-T(Digital Video Broadcasting-Terrestrial)标准,日本的ISDB-T(Integrated Services Digital Broadcasting-Terrestrial)标准,以及美国的ATSC(Advanced Television Systems Committee)标准等[1]。

目前,支持多协议多标准的宽带数字电视调谐器得到了越来越广泛的研究。 地面数字电视标准规定的信号频率范围为48-900MHz,涵盖VHF/UHF频段。很 多标准协议采用正交分频复用(Orthogonal Frequency Division Multiplexing)的 调制方式,它对系统的I/Q失配以及相位噪声等性能有着较高的要求。频率综合 器作为宽带数字电视调谐器中的关键模块,为其提供低噪声,低杂散,高频谱纯 度的本振信号(Local oscillator, LO)。

随着CMOS工艺的不断发展,人们对芯片的集成度、低功耗以及稳定性的要求越来越高,这也迫使者设计者不断去优化改进电路。应用于电视调谐器中的频率综合器经历了从早期手动的旋转式调谐器,到现在基于锁相环结构的频率综合器,在频率精度、频率步长、相位噪声以及稳定性等方面有了长足的进步。在系统理论等方面,Floyd M.Gardner[2], Venceslav F.Kroupa[3]和Dean Banerjee [4]等前辈的卓越贡献使得频率综合器这门技术也越来越多地被设计者所掌握。

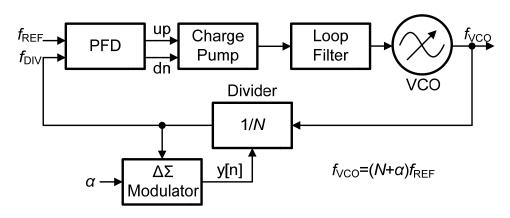

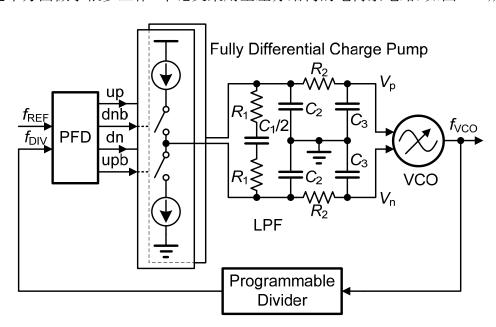

图 1-1 ΔΣ 分数分频频率综合器

目前在商用的电视调谐器中,应用最广泛的是采用 $\Delta\Sigma$ 调制器(Delta Sigma Modulator, DSM)的分数分频频率综合器,如图1-1所示。它通过 $\Delta\Sigma$ 调制器输出

的量化序列动态地调整分频比,从而实现分数分频。分数的小数部分越小,频率精度也就越高。输出频率精度也就不再受限于参考时钟频率,这为选取较大的环路带宽来提高锁定速度提供了方便。当然, $\Delta\Sigma$ 分数分频频率综合器也存在许多问题需要解决,譬如 $\Delta\Sigma$ 调制器引入的量化噪声、环路的非线性等。

## 1.2 论文的主要贡献

本论文主要设计了 ΔΣ 分数分频频率综合器中的鉴频鉴相器、电荷泵、分频器以及 I/Q 分频器等电路模块。针对设计中遇到的问题,采用了相应的技术和解决办法,本论文的主要贡献有:

- 1) 分析了电荷泵型鉴频鉴相器的非线性对带内噪声的影响,提出了一种降低非 线性的技术来减小鉴频鉴相器和电荷泵对带内噪声的贡献。

- 2) 在鉴频鉴相器的设计中,同时引入两种工作模式:一种是基于传统的工作模式,并且导通时间可供选择;另外一种是基于降低电路非线性的工作模式。此外,本论文还设计了重置信号开关电路和锁定检测电路,用于环路的控制。

- 3) 采用全差分结构的电荷泵,来提高频率综合器的性能。设计的源端开关型电荷泵单元简化了电路,并且使得电荷泵上下电流的调节来得更为简单。

- 4) 把整个全差分电荷泵的有源电路版图置于环路滤波器的 MIM(Metal Insulator Metal)电容之下,用第三铝金属层作为隔离层,使得电荷泵和环路滤波器的芯片面积减小近二分之一。

- 5) 详细分析了晶体管间的 mismatch 对电荷泵电路性能的影响,得出了晶体管间的 mismatch 在整个电荷泵上下电流匹配特性中占主要地位的结论。

- 6) 设计了一种全新的 I/Q 分频器电路,可以减小工艺误差对电路性能的影响。 其间,引入一个对输入信号放大整形的电路,很好地解决了困扰电路的灵敏 度问题。

# 1.3 论文的研究内容和组织结构

本论文主要介绍了 ΔΣ 分数分频频率综合器中几个模块的设计,包括鉴频鉴相器、电荷泵、分频器和 I/Q 分频器电路模块。论文从频率综合器的性能要求出发,分别指出各个模块设计中所要考虑的因素,并提出相应的解决方案。论文各部分内容安排如下:

第二章"频率综合器"首先阐述了频率综合器的原理;然后指出频率综合器设计时需要关注的几个重要参数,分析了这些参数的影响并且给出了相应的推导过程;最后总结了频率综合器的设计流程。

第三章"鉴频鉴相器分析与设计"首先介绍了鉴频鉴相器的电路结构;然后 分析了鉴频鉴相器中的非理想效应,相位噪声模型以及非线性特性,并且提出了 相应的改进方案,包括提出的一种降低非线性的技术,最后给出了具体的鉴频鉴相器的电路版图和仿真结果。

第四章"全差分电荷泵设计"首先分析了基于全差分电荷泵电路的环路稳定特性;然后从晶体管级别分析了影响电荷泵性能的一些考虑因素,其中对晶体管间的 mismatch 做了详细的分析;最后给出了全差分电荷泵的电路版图和仿真结果。

第五章"分频器分析与设计"介绍了基于高速电流模式(Current Mode Logic, CML)结构的 4/5 预分频器和 I/Q 分频器的设计。分别对 4/5 预分频器的时序问题和 I/Q 分频器的匹配特性进行了详细分析并且给出了相应的解决方法。设计了一种全新的 I/Q 分频器电路,解决了困扰电路的灵敏度问题。最后,给出了 4/5 预分频器和 I/Q 分频器的电路版图和仿真结果。

第六章 "展望与总结" 首先对本文的工作进行总结, 然后对未来的工作进行 了简单的展望。

# 第二章 频率综合器概述

## 2.1 引言

随着移动终端的飞速发展,便携式的电子产品已经明显改变了人们的生活方式。诸如智能手机的普及,人们习惯性地通过 3G 等无线网络连接到互联网,使得无线通讯市场蓬勃发展。被誉为电子系统"心脏"的频率综合器在通讯领域得到了越来越广泛的重视。

频率综合器可以产生一个或多个频率信号,为数字系统和射频接受发送器提供时钟信号或者本振信号。按照实现结构分,频率综合器可以分为直接数字频率综合器和锁相环频率综合器。直接数字频率综合器基于全数字技术,将抽样正弦波形存在存储器中,直接合成所需频率的波形。它具有速度快、频率分辨率高等优点。但是它的功耗比较大而且频率范围受到限制。锁相环频率综合器通过反馈环路能够得到高纯度的输出频谱,而且很容易得到不同频率的信号,所以得到了广泛的应用。

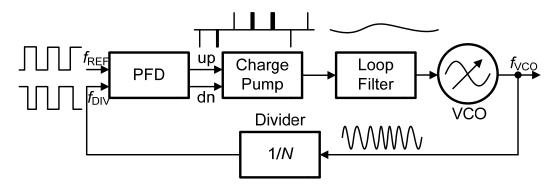

## 2.2 频率综合器

整数分频频率综合器的结构相对简单,如图 2-1 所示。实质上,频率综合器是一个基于相位的负反馈系统。它的工作过程,大致可以描述如下:鉴频鉴相器检测来自参考时钟与分频器输出的频率信号,比较它们的相位差,并把相位差转换成两路数字脉冲信号。通过这两路数字信号分别去控制电荷泵的上下导通开关,使得电荷泵产生相应的电流。这些电流注入到环路滤波器(Loop Filter, LPF)中,导致环路滤波器电容上的电荷不断积累,从而完成了电流到电压的转换。压控振荡器(Voltage Control Oscillator, VCO)具有近似线性的调控特性,能够把环路滤波器的电压转换成相应的频率。但是压控振荡器的频率很高,需要分频器对其分频处理后,才能与参考时钟频率比较。这样就完成了一个循环的过程。

图 2-1 整数分频频率综合器

分频器作用于频率综合器的反馈环路上,分频比为 1/N。就如同运放中的反馈系数  $\beta$ ,放大倍数为反馈系数的倒数  $1/\beta$ 。在这里,压控振荡器的输出频率  $f_{VCO}$ 为参考时钟频率  $f_{REF}$  的 N 倍

$$f_{\text{VCO}} = N \times f_{\text{RFF}} \tag{2.1}$$

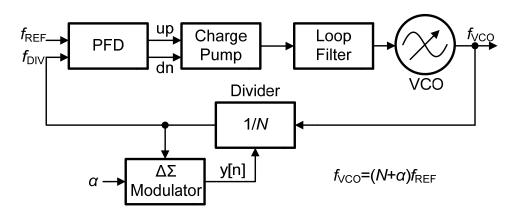

然而,整数分频频率综合器的性能受到参考频率  $f_{REF}$  的限制。一方面, $f_{REF}$  决定了频率综合器能够达到的最小精度, $f_{REF}$  不能选得太大;另一方面, $f_{REF}$  也决定了环路的带宽( $f_{BW} < f_{REF} / 10$ ), $f_{REF}$  不能选得太小。因为,环路带宽太小会减慢环路的锁定时间,而且对抑制压控振荡器在环路中贡献的噪声不是很理想[5]。考虑到上述问题,工程中应用的更多的是分数分频频率综合器,其结构如图 2-2 所示。

图 2-2 分数分频频率综合器

与整数分频频率综合器采用整数分频比不同,分数分频频率综合器在环路锁定之后,  $f_{DIV}$  的边沿不是严格对齐  $f_{REF}$  的边沿,而是时而超前,时而滞后。只是 $f_{DIV}$  边沿的平均值与  $f_{REF}$  的边沿对齐。所以,分数分频实现的是一种动态的锁定。但这又引入了另外一个问题"分数毛刺"。当相位差增加到一个不可忽略的值时,低通滤波器输出的幅值也变得相当大,使得分数毛刺的幅值仅仅比载波信号低20~30dB[7]

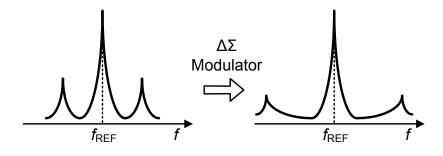

为了解决上述问题,在分数分频频率综合器的设计中应用到了 ΔΣ 调制器,它在对输入信号过采样的同时,将低频的量化噪声搬移到较高的频率,通过对量化噪声整形,可以进一步提高带内的信噪比,如下图 2-3 所示。

$\Delta\Sigma$  调制器[6]输出整数序列 y[n],在信号  $f_{DIV}$  的协调下,控制多模分频器的分频比 N+y[n]。输入信号  $\alpha$  介于 0 和 1 之间,在锁相环锁定之后,y[n]长时间的平均值即为  $\alpha$ 。于是我们得到输出频率  $f_{VCO}$  为参考时钟频率  $f_{REF}$  的  $N+\alpha$  倍

$$f_{\text{VCO}} = \left(N + \frac{1}{n} \sum_{k=1}^{n} y[k]\right) \times f_{\text{REF}} = \left(N + \alpha\right) \times f_{\text{REF}}$$

(2.2)

图 2-3 ΔΣ 调制器对噪声的整形

需要注意的是,如果环路中各个模块的非线性表现得比较明显,**ΔΣ** 调制器 对噪声的整形也将被恶化。带外的量化高频噪声将会被折叠到低频的带内,增加 带内的相位噪声和毛刺成分[**8**]。

# 2.3 重要参数

频率综合器的设计需要考虑很多影响系统性能的因素,并且它们之间相互影响,使得设计变得复杂。于是,我们有必要对这些因素进行简要说明,在理解它们的基础上为后面几个章节的电路分析和设计提供指导。本小节我们主要介绍几个重要的品质因素:相位噪声(Phase Noise)、毛刺(Spurious Emissions)和锁定时间(Lock Time)[9]。

#### 2.3.1 相位噪声

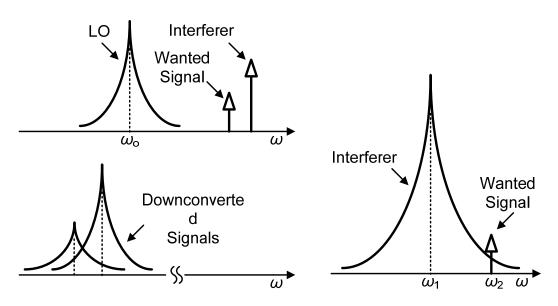

接收机的本振输出包含相位噪声,则通过互易混频使得很强的临近干扰信号也同时被变换到有用信道中,造成信号频谱的阻塞,降低了信道中的信噪比,如图 2-4(a)所示。即使中频滤波器能够滤除强干扰中频信号,强干扰中频信号的噪声边带仍然淹没了有用信号,使接收机无法接收到弱小信号,如图 2-4(b)所示。

#### (a) 本振相噪下变频影响信噪比

(b)干扰信号相噪直接影响有用信道

图 2-4 相位噪声的影响

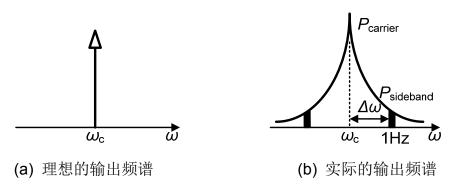

那么什么是"相位噪声"?简单的说,譬如有一个周期性的正弦信号,x(t) =  $A\cos[\omega_c t + \Phi_n(t)]$ ,其中  $\Phi_n(t)$ 表示一个周期中变化的相位量,而我们就把这个  $\Phi_n(t)$ 称为"相位噪声"。相位噪声通常在频域中表征。对于一个理想的振荡器,其频谱表现为单一频率,如图 2-5(a)所示;而在实际的振荡器中,其频谱则表现为载频附近的裙状,如图 2-5(b)所示。

图 2-5 相位噪声

为了比较相位噪声的大小,需要量化相位噪声。通常,相位噪声被定义为偏离载波附近  $\Delta\omega$  处 1HZ 内单边带噪声功率  $P_{\text{sideband}}$  与载波功率的  $P_{\text{carrier}}$  比值,用 dBc/Hz 表示

$$\mathcal{L}\left\{\Delta\omega\right\} = 10 \cdot \log \left[\frac{P_{\text{sideband}}\left(\omega_0 + \Delta\omega, 1\text{Hz}\right)}{P_{\text{carrier}}}\right]$$

(2.3)

在频率综合器的设计中,为了量化各个模块的相位噪声在整个环路中的贡献,本论文参考了 MIT 的 Perrot 教授提出的相噪模型。其主要思路:基于整个环路的传递函数,把各个模块的噪声贡献通过相应的传递函数在输出端求和,得到最终输出的相位噪声[10]。

图 2-6 整数分频频率综合器的 s 域模型

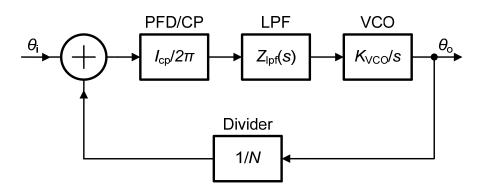

为了方便传递函数的计算,以整数分频频率综合器为例,如图 2-6 所示。

$I_{cp}/2\pi$  表示 PFD/CP 的转换增益,其中  $I_{cp}$  是电荷泵电流; $Z_{lpf}(s)$ 表示滤波器的输入电流到输出电压的传递函数; $K_{VCO}/s$  表示压控振荡器的输入电压到输出频率的传递函数,其中  $K_{VCO}$  是调谐增益;1/N 表示反馈回来中的传递函数,N 是分频器的分频比。

实际上,鉴于 PFD/CP 的开关采样特性,采用 z 域的离散模型才能更真实地反映频率综合器的工作过程[11]。但是,当环路带宽小于参考频率的十分之一时,为了方便分析,用 s 域模型已经可以得到很好的近似[12]。

参考图 2-6 中整数分频频率综合器的 s 域模型,得到它的开环传递函数 G(s)和反馈回路的增益函数 H(s)

$$G(s) = \frac{I_{cp} \cdot Z_{lpf}(s) \cdot K_{vco}}{2\pi \cdot s}$$

(2.4)

$$H(s) = \frac{1}{N} \tag{2.5}$$

进一步得到闭环环路的传递函数

$$F(s) = \frac{G(s)}{1 + H(s) \cdot G(s)}$$

(2.6)

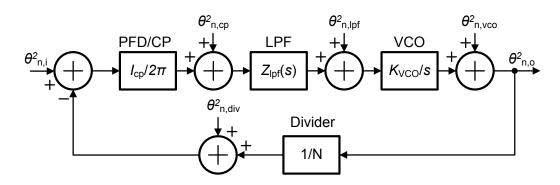

每个模块对整个环路的相位噪声贡献,可以通过把它的相位噪声等效到相应模块的输入,然后经过传递函数在输出端累加得到,如图 2-7 模型所示。其中, $\theta^2_{n,i}$ 是参考时钟的等效输入噪声, $\theta^2_{n,cp}$ 是鉴频鉴相器和电荷泵的等效输出噪声, $\theta^2_{n,lpf}$ 是环路滤波器的等效输出噪声, $\theta^2_{n,voo}$ 和  $\theta^2_{n,div}$ 分别是压控振荡器和分频器的等效输出噪声。

图 2-7 整数分频频率综合器相位噪声模型

在输出频率相对较高的频率综合器中,采用较多的是无源滤波器。为了简化模型,我们用 *T*(s)表示滤波器中电阻噪声的传递函数。类似前面的分析,我们可以得到各个模块噪声在输出端的贡献

$$\theta_{n,o}^{2} = \theta_{n,i}^{2} \cdot \left| \frac{NH_{o}(s)}{1 + H_{o}(s)} \right|^{2} + \theta_{n,cp}^{2} \cdot \left| \frac{NH_{o}(s)}{1 + H_{o}(s)} \cdot \frac{2\pi}{I_{cp}} \right|^{2} + \theta_{n,lpf}^{2} \cdot \left| \frac{K_{vco}}{s} \frac{s}{1 + H_{o}(s)} \right|^{2} + \theta_{n,vco}^{2} \cdot \left| \frac{1}{1 + H_{o}(s)} \right|^{2} + \theta_{n,div}^{2} \cdot \left| \frac{NH_{o}(s)}{1 + H_{o}(s)} \right|^{2}$$

(2.7)

通过具体分析上式的传递函数,我们可以得到以下结论:参考时钟、分频器以及鉴频鉴相器和电荷泵的噪声传递函数呈低通特性;环路滤波器的噪声传递函数呈带通特性;而压控振荡器的传递函数本身呈高通特性。需要注意的是,压控振荡器的噪声随着频偏的增加逐渐减小,以至于在整个传递函数中表现带通。

图 2-8 频率综合器各模块的噪声分布

图 2-8 考虑了上述各个模块的噪声分布,然后在输出端得到的拟合图形。我们可以看到在频偏较低处,主要受到参考时钟噪声的影响;在频偏更远处,主要受到鉴频鉴相器和电荷泵的噪声的影响;在环路带宽的转折点或略高处,则主要受到压控振荡器和环路滤波器噪声的影响。另外,如果是分数分频的频率综合器,在带外还会有一个额外的凸起,甚至可能超过环路带宽内的噪声。

#### 2.3.2 毛刺

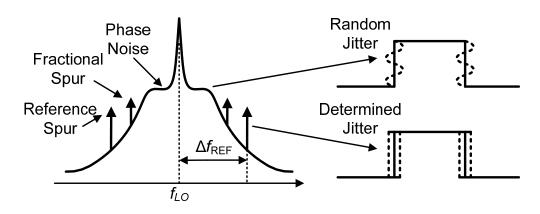

在理想情况下,我们需要在频率综合器的输出端得到单一频率的信号,但是由于相位噪声和其他非理想因素的作用,实际输出的频谱如图 2-9 所示[13]。其中在某些频偏上有明显的调制频率成分,称为"毛刺"。为了形象地描述这些毛刺的影响,图右侧给出了它在时域中的抖动情况。

本小节主要介绍了  $\Delta\Sigma$  分数分频频率综合器中的两个系统毛刺:分数毛刺 (Fractional Spur)和参考毛刺(Reference Spur)。

图 2-9 输出频谱与波形的抖动

#### 1) 分数毛刺

对于一个理想的噪声整形电路, $\Delta\Sigma$  调制器的输出应该只会出现较小的毛刺。但是当  $\Delta\Sigma$  调制器的输入信号为分数时,它在数字电路中只能依靠移位来实现。一定的截断误差削弱了输出序列的随机性。大多数  $\Delta\Sigma$  分数分频频率综合器的输出频谱中,除了有统计分布的抖动以外,还会在某些频点上出现毛刺,称为"分数毛刺"。分数毛刺与参考时钟频率有以下关系,如公式(2.8)所示,其中 B 是  $\Delta\Sigma$  调制器中计数器的大小,M 是  $\Delta\Sigma$  调制器的输入,以及参考时钟频率  $f_{REF}$

$$f_{spur} = \frac{M}{2^{B}} \cdot f_{REF} \tag{2.8}$$

一般来说,环路带宽要远小于参考时钟频率。参考毛刺得到很大抑制,因此分数毛刺成为主要考虑的问题。

#### 2) 参考毛刺

在分数分频频率综合器中,由于参考时钟对环路滤波器的调制,在载波频偏  $\pm f_{REF}$  及其谐波处,仍旧存在着参考毛刺。这些参考毛刺的存在,主要是由于电荷泵的泄露电流以及上下电流的不匹配导致在鉴频鉴相器输入端存在静态的相位差  $\Delta \theta$ ,并且通过压控振荡器的调制产生。参考毛刺贡献的相位噪声如公式(2.9) 所示

$$\mathcal{L}(n \cdot f_{REF}) = 20 \log \left( \frac{I_{I} \cdot Z_{Ipf}(n \cdot f_{REF}) \cdot K_{vco}}{n \cdot f_{REF}} \right)$$

(2.9)

其中, $I_1$ 是电荷泵的泄流电流, $Z_{lpf}(s)$ 是环路滤波器的传输函数, $K_{vco}$ 是压控振荡器的增益, $nf_{REF}$ 表示了参考频率的整数倍谐波。当环路锁定后,电荷泵的泄漏电流可以忽略,此时电荷泵的上下电流不匹配占主导。但是,随着器件的尺寸越来越小,在有效沟道小于 100nm 后,泄漏电流变得越来越大,其影响就不可忽略了。

相比较于整数分频频率综合器,分数分频频率综合器的环路是动态锁定的,而且环路带宽相对较大,对毛刺的抑制相对较小,所以它的参考毛刺也大得多。

#### 2.3.3 锁定时间

除了相位噪声和毛刺,频率综合器的锁定时间也是一个非常关键的参数。简单的说,锁定时间表征了一个频率综合器能够切换频率的快慢程度,一般要求在几十毫秒到几十微秒的范围内[7]。

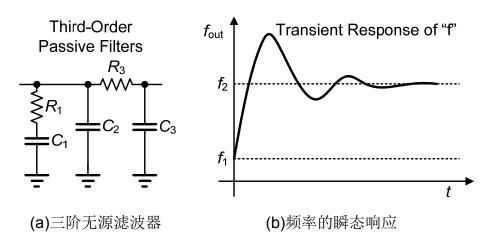

当频率综合器的输出频率从  $f_1$  变化到  $f_2$ 时,参考时钟的频率也从  $f_4/N$  变化到  $f_2/N$ ,近似于一个阶跃函数。通过对阶跃函数进行拉普拉斯变换并且结合闭环传递函数(2.6),然后对其进行反傅里叶转换,得到输出频率随时间变化的函数。为方便起见,以三阶无源滤波器为例,如图 2-10(a)所示。

$$F(t) = f_2 + (f_1 - f_2) \cdot e^{-\xi \cdot \omega_n \cdot t}$$

$$\cdot \left[ \cos\left(\omega_n \sqrt{1 - \xi^2} \cdot t\right) + \frac{\xi - R_2 \cdot C_2 \cdot \omega_n}{\sqrt{1 - \xi^2}} \cdot \sin\left(\omega_n \sqrt{1 - \xi^2} \cdot t\right) \right]$$

(2.10)

其中  $\omega_n$  和  $\xi$  分别表示系统的本振频率和瞬态响应的阻尼因子,它们的值可以分别通过公式(2.11)和公式(2.12)得到

$$\omega_n = \sqrt{\frac{I_{cp} \cdot K_{VCO}}{2\pi \cdot N \cdot (C_1 + C_2 + C_3)}}$$

(2.11)

$$\xi = \frac{R_2 \cdot C_2}{2} \cdot \omega_n \tag{2.12}$$

最后,从公式(2.10)我们可以得到频率综合器的输出频率从  $f_1$  变化到  $f_2$  所需的锁定时间,其中  $\Delta f = f_2 - f_1$

$$T_{L} = \frac{-\ln\left(\frac{\Delta f}{f_{2} - f_{1}} \cdot \frac{\sqrt{1 - \xi^{2}}}{1 - 2 \cdot R_{2} \cdot C_{2} \cdot \xi \cdot \omega_{n} + R_{2}^{2} \cdot C_{2}^{2} \cdot \omega_{n}^{2}}\right)}{\xi \cdot \omega_{n}}$$

(2.13)

图 2-10 (b)形象地描述了输出频率  $f_1$  变化到  $f_2$  的瞬态过程。

图 2-10 输出频率的瞬态响应

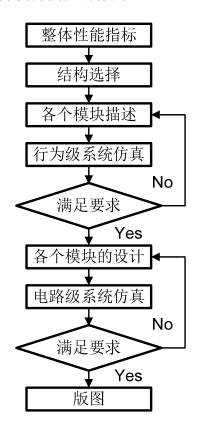

### 2.4 设计流程

频率综合器的设计是一个复杂的过程。其中电荷泵和滤波器属于模拟电路的范畴; 压控振荡器属于射频电路的范畴; 鉴频鉴相器和分频器可以调用数字单元直接实现; 而自动增益控制模块以及 I<sup>2</sup>C 电路则可以由数字综合直接得到。下面我们简单介绍下频率综合器的设计流程:

第一步,根据实际应用的要求,定出频率综合器需要达到的性能指标。其中有些可以直接得到,有些需要参考一些文档并通过推断计算才能得出。以下列出了主要的几个设计指标:

- a) 输出频率

- b) 带内和带外噪声

- c) 最大容许的毛刺水平

- d) 锁定时间

第二步,选择具体实现频率综合器的结构。频率综合器的结构多种多样,各有各的优势和缺点,结合具体的工艺技术特点,需要具体评估。

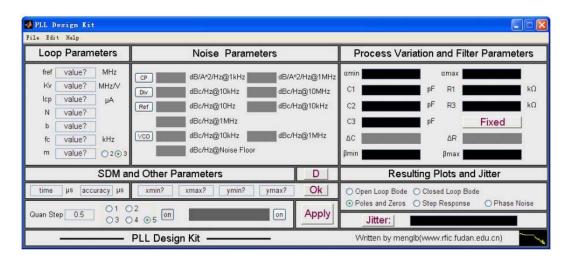

第三步,根据前面所确定的整体性能指标和结构,计算出各个模块的详细设计参数。这是一个反复修改的过程,为了提高某个性能而优化某个参数的时候,同时也会影响环路的其他特性。为了方便计算,我们根据环路参数分析和相噪模型,利用 MATLAB 编写了一个 PLL Design Kit 工具包,其界面如图 2-11 所示。设计者只需输入开环传递函数的相关参数,程序就会自动计算出滤波器的参数,得到环路的闭零极点分布、频率响应和阶跃响应。同样,设计者只需输入子模块在相应频点处的噪声值,程序会自动拟合该模块的噪声曲线并进行环路相位噪声的分析。

图 2-11 PLL Design Kit

第四步,在系统行为级仿真正确的前提下,可以利用 Cadence, Hspice 等

电路设计软件,可以开始具体电路模块的设计。其间会遇到诸多问题,譬如理论的论证,电路的可实现性,性能之间的折中,以及非理想因素的制约等等。

第五步,在各个模块成功设计的基础上,需要通过仿真确认整个环路的性能, 看是否满足最初的设计要求。即便各个模块的性能基本达到,但是通过联仿还会 遇到很多问题,需要回到第四步,反复修改电路,直到整个系统满足要求。

图 2-12 是一个简单的设计流程,完成整个频率综合器的设计需要团队成员间相互协调,相互帮助,充分发挥团队的作用。

图 2-12 频率综合器设计流程

# 2.5 本章小结

- 1) 首先介绍了两种类型的频率综合器,整数分频频率综合器和分数分频频率综合器,并且指出了各自存在的问题。

- 2) 然后本章重点分析了在频率综合器的设计中需要关注的几个参数,包括各个模块的相位噪声,输出频谱中的毛刺以及环路的锁定时间。

- 3) 最后总结了频率综合器设计的各个步骤,给出了一个简要的设计流程图。

# 第三章 鉴频鉴相器分析与设计

## 3.1 引言

锁相环本质上是一个比较相位的负反馈系统。鉴相器比较反馈环路和参考时钟的相位差,产生与之成比例的脉冲信号。然而,鉴相器对于两个输入信号的频率范围有一定的要求。如果频率相差太大超过环路带宽,就不能正常锁定,这个就是通常所说的"锁定捕获问题"[2]。为了解决这个问题,人们在检测相位的基础上又引入了一个检测频率的辅助电路,这样的电路被称为"鉴频鉴相器"。

考虑到鉴频鉴相器和电荷泵的非线性对频率综合器性能的影响,论文提出了一种降低非线性的技术。但保留了传统的工作模式。考虑到导通时间  $t_{on}$  对带内噪声的影响,在电路中添加了可以选择导通时间的功能。所以,本论文设计的鉴频鉴相器有多种工作模式可供选择。

#### 3.2 PFD/CP

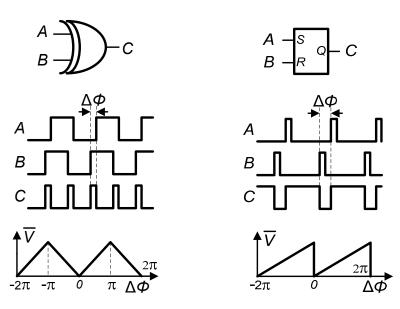

鉴频鉴相器可以采用数字单元直接实现,它的工作频率高,功耗低。按电路的结构分,鉴频鉴相器主要有四种结构[9]。

第一种是异或门 XOR 结构型鉴相器,它的平均电压值与相位差成正比,如图 3-1(a)所示。异或门电路对两个输入端口上升沿和下降沿都产生误差脉冲,而其他的鉴相器可能只是对正边沿或者负边沿产生响应,不过它的最大工作范围只有 180°,只能检测到 180°范围内的剩余相位,这个也是它被很少采用的原因。

图 3-1 异或门型和触发器型鉴相器

(b) 触发器型鉴相器

(a) 异或门 XOR 型鉴相器

第二种是基于 SR 触发器的鉴频鉴相器,它的平均电压值也跟相位误差成正比,如图 3-1(b)所示。相比于异或门型鉴相器,它的工作范围为 360°。

第三种是基于乘法器型。假设有两个正弦信号  $x_1=A_1\cdot\sin(\omega_1+\theta_1)$ 和  $x_2=A_2\cdot\sin(\omega_2+\theta_2)$ ,它们经过乘法器混频后,得到输出信号

$$v_{d} = A_{d} \cdot \left\{ \sin \left[ \left( \omega_{1} - \omega_{2} \right) \cdot t + \theta_{1} - \theta_{2} \right] + \cos \left[ \left( \omega_{1} + \omega_{2} \right) \cdot t + \theta_{1} + \theta_{2} \right] \right\}$$

(3.1)

其中  $A_d$ = $A_1$ · $A_2$ /2。在频率锁定的情况下, $\omega_1$  与  $\omega_2$  的差值为零,所以乘法器型鉴相器的输出信号是  $A_d$ · $\sin(\theta_1-\theta_2)$ 。它是一个与( $\theta_1$ - $\theta_2$ )成比例的直流分量。这种结构的鉴相器在输入频率很高的时候比较适用,但是它会在输出端产生不必要的毛刺成分(特别是在  $\omega_1$ + $\omega_2$  频率处),会进一步恶化相噪。

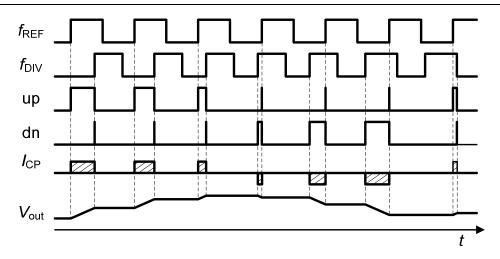

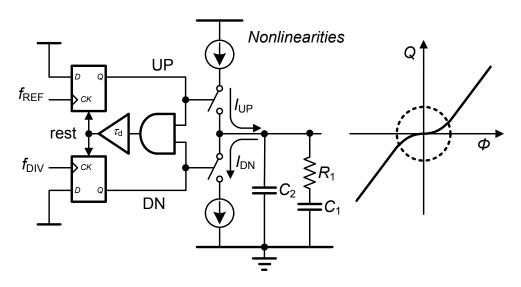

第四种是基于电荷泵型的鉴频鉴相器,也是被广泛应用的一种结构,如图 3-2 所示。它由两个边沿触发、带复位的 D 触发器和一个逻辑与门组成,其中触发的 D 输入端都接逻辑 "1"。 f<sub>REF</sub> 表示参考时钟信号,一般由片外的晶体振荡器产生,具有相当稳定的频率。 f<sub>DIV</sub> 表示分频器的输出信号。由于压控振荡器的输出频率很高,需要对其进行分频处理才能与较低频率的参考时钟信号 f<sub>REF</sub> 比较。

图 3-2 电荷泵型鉴频鉴相器 PFD/CP

它的工作原理: 两个输入 f<sub>REF</sub> 和 f<sub>DIV</sub> 中任意一个信号波形的上升沿到来时,该信号便会触发相应的 D 触发器。输出变为高电位,然后去控制相应的电荷泵开关,使得对应支路的电流导通。直到另外一个信号波形的上升沿到来后,它同样会触发相应的 D 触发器,使得输出也变为高电位。这时候,逻辑与门便检测到两个同时为高的信号,逻辑与门的输出为高电位,重置两个 D 触发器(假设 D 触发器是高电位复位),使得它们的输出重新变为低电位。电荷泵的开关也就被重新关断,其工作过程如图 3-3 所示。

图 3-3 PFD/CP 工作过程

从上图可以看出,鉴频鉴相器和电荷泵表现的增益是无穷大的。只要它的输入相位差不为零,就会导致不断有电荷在环路滤波器的电容上积累。所以在相位锁定时,输入相位误差必须精确地等于零。

基于电荷泵型鉴频鉴相器主要有以下优势:

- a) 剩余相位检测范围为 360°, 在该范围内都具有较好的线性特性;

- b) 解决了锁相环中的锁定捕获问题,扩展了频率的捕捉范围。

在实际的电路设计中,还有很多非理想因素需要考虑。电荷泵和鉴频鉴相器的非线性也严重影响输出的相位噪声,下面就这些问题展开讨论。

## 3.3 设计考虑

#### 3.3.1 非理想效应

即使在环路锁定的情况下,由于鉴频鉴相器和电荷泵的一些非理想特性的存在,会引起压控电压产生很大的波纹。而这个波纹通过压控振荡器的调制,又会在输出频谱上产生不必要的频率成分。其中这些非理想的因素包括:死区效应(Dead-zone),上下开关的延时差异以及电荷共享效应等。

图 3-4 PFD/CP 的死区效应

由于电荷泵开关结点存在若干寄生电容,所以会有一定的上升时间和下降时间。如果鉴频鉴相器检测到的相位差  $\Delta \phi$  太小,提供的 up 和 dn 信号脉冲宽度便不足以开启电荷泵,也就没有电流注入到环路滤波器中,这个就是所谓的"死区效应",如图 3-4 所示。而这个区域的非线性将严重恶化环路的相位噪声,这在后面小节会详细讨论。

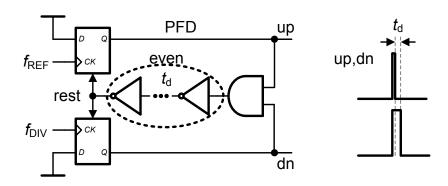

为了消除死区效应,通常的方法是在 D 触发器的复位信号前串入偶数个反相器,如图 3-5 所示。它主要通过增加了从逻辑与门到 D 触发器复位端口间的延迟时间  $t_d$ ,使得 up 和 dn 开关信号增大一个  $t_d$  时间的脉冲宽度,从而保证有足够的时间去开启电荷泵。

图 3-5 死区效应的消除方法

另外,电荷泵充电电流开关使用 PMOS 晶体管,而放电电流开关使用 NMOS 晶体管,两种开关管的类型不一样,如图 3-6 所示。所以从鉴频鉴相器出来的 up 信号必须低电位有效,而 dn 信号必须高电位有效。于是需要在 up 信号的通路中引入一个反相器,这样就造成了 up 和 dn 两条通路上的延迟时间不相同。而这个延时的差异表现在电荷泵的充放电工作中,就会有一个周期性的相位差。同样也会在压控振荡器的输出端产生参考毛刺。

图 3-6 鉴频鉴相器上下开关的延时差异

比较常用的方法是在 dn 信号通路中额外引入一个延迟时间跟反相器差不多

的传输门,来减延迟时间不同的影响。

但是,本论文采用的是全差分的电荷泵结构,需要两组开关分别去控制各自支路,如图 3-7 所示。考虑到延迟平衡的问题,两条通路分别采用交叉耦合的反相器。一方面,是为了互补特性的考虑;另一方面,两条通路采用完全相同的电路结构,使得 up 信号和 dn 信号通路之间的延时问题得到很好地解决。

图 3-7 延迟平衡的差分输出鉴频鉴相器

另外一个比较重要的非理想效应是电荷共享[14]。由于电流源的漏端存在一定的电容,在开关导通的瞬间,就会有电荷在漏端电容和环路滤波器上的电容之间重新分布。这个分布的情况不仅跟漏端电容的大小有关,也与输出端电压的大小有直接的关系。结果是在开关的瞬间,会在压控电压处有明显的跳动。本文设计的电荷泵采用的是源端开关,并且在输出端与开关管子之间串入一对共源共栅管,起到了很好的隔离作用。所以电荷共享效应不是很严重。

#### 3.3.2 PFD/CP 的相位噪声

鉴频鉴相器对频率综合器的相噪贡献是相当大的,尤其是带内噪声。在已发表的关于相位噪声研究的文献中,其中有两个模型给我们提供了很好的帮助。

第一个模型由 Cranincks[15]提出,它是基于电荷泵导通时产生的电流( $I_{CP}$ ) 噪声来估计鉴频鉴相器噪声的。在环路锁定的情况下,电荷泵可以被看成一个稳定的电流噪声源,电流噪声大小由公式(3.2)给出。其中  $I_{cp}$  为电荷泵的上下电流, $\alpha_{cp}$  表示一个周期中的导通时间所占得比例, ( $V_{cs}$ - $V_t$ ) $_{cp}$  是 MOS 管栅源电压与电荷泵电流源晶体管的阈值电压之差

$$\frac{\overline{i^2}}{\Delta f} = 2 \cdot \alpha_{cp} \cdot 4 \cdot k \cdot T \cdot \frac{2 \cdot I_{cp}}{\left(V_{GS} - V_t\right)_{cp}}$$

(3.2)

虽然上式是通过电荷泵的电流噪声来计算鉴频鉴相器的相位噪声,而不是独立得到。但是它还是可以用来计算鉴频鉴相器和电荷泵在整个频率综合器中的贡献,如公式(3.3)所示(当频偏  $\Delta \omega$  明显小于环路带宽  $\omega_c$  的时候才有效)。

$$\ell\left\{\Delta\omega\ll\omega_{c}\right\} = \frac{1}{2}\cdot\left(2\cdot\pi\cdot\frac{N}{I_{cp}}\right)^{2}\cdot2\cdot\alpha_{cp}\cdot4\cdot k\cdot T\cdot\frac{2\cdot I_{cp}}{\left(V_{GS}-V_{t}\right)_{cp}}\tag{3.3}$$

从表达式可以看出如果想减小相位噪声,可以通过减小电荷泵中电流源的晶体管( $V_{cs}$ - $V_t$ ) $_{cp}$ ,也可以通过减少一个周期中电荷泵的导通时间或者选择合适的电电荷泵电流  $I_{cp}$  来实现。

另一个模型由 Banerjee[16]提出,它通过在环路输出端得到参数  $L_{1Hz}$  来估计鉴频鉴相器的相位噪声。该参数表示在参考频率为 1Hz 时环路带宽内( $\omega \ll \omega_c$ )的噪声水平。该范围内除了鉴频鉴相器外,还包含其他诸如压控振荡器、晶体振荡器等噪声。但鉴频鉴相器的相位噪声却是最重要的,其他的可以忽略,所以这也为估算这个参数  $L_{1Hz}$  变得可靠有效。由公式(3.4)可以得到参数  $L_{1Hz}$  大概的值,其中 N 是 PLL 的分频比, $f_{RFF}$  是参考频率,

$$\mathcal{L}\{\Delta\omega\ll\omega_c\} = L_{\text{Hz}} + 10\cdot\log(f_{RFF}) + 20\cdot\log(N) \tag{3.4}$$

需要注意的是,虽然这个参数使得在不同参考频率下比较频率综合器的性能 成为可能,但是它仍然是个经验参数。这也影响了它在实际应用中的参考价值。

#### 3.3.3 非线性考虑

如果整个环路中各个模块的非线性表现得比较明显,带外的量化高频噪声将会被折叠到低频的带内,增加了带内的相位噪声和毛刺成分。这个问题已经在文献[17]中详细地讨论过。为了控制量化噪声的分布,通常采用低阶的  $\Delta\Sigma$  调制器(较小的  $\Delta\Sigma$  抖动),同时优化各个模块的线性特性。

环路中的非线性问题,主要来自于鉴频鉴相器和电荷泵的 I/O 传输特性,其中包括鉴频鉴相器中的死区、电荷泵的漏电流、电荷泵上下电流源的不匹配以及电荷泵的开关瞬间不匹配等[18]。

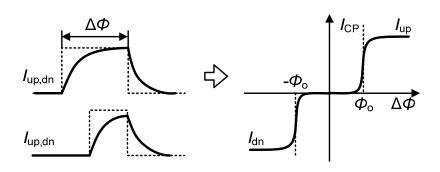

图 3-8 PFD/CP 的非线性

一个典型的鉴频鉴相器和电荷泵电路,如图 3-8 所示。其中非线性最严重的部分也就是输入相位误差比较小的过零点位置。即便引入了降低非线性的技术,它对带内噪声的影响还是很大的[19]。下面通过对电荷泵上下电流的建模,来量化的分析非线性的产生过程。

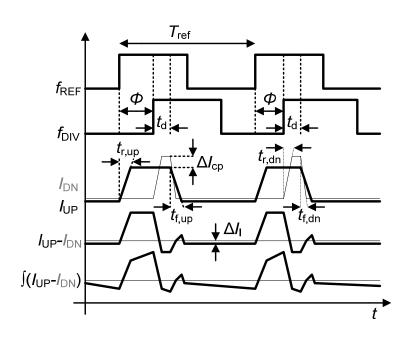

图 3-9 PFD/CP 输入输出的时序波形

鉴频鉴相器检测参考时钟与分频器出来相位误差  $\boldsymbol{\phi}$ ,经过电荷泵作用后产生的波形,如图 3-9 所示。其中  $I_{UP}$  和  $I_{DN}$  分别表示电荷泵的上下电流。由于它们的开关不同,所以开启时间和关断时间也不一样, $t_{f,up}$  和  $t_{f,up}$  分别是  $I_{UP}$  电流的上升和下降时间常数。同样的, $t_{f,dn}$  分别表示  $I_{DN}$  电流的上升和下降时间常数。 $t_{d}$  是鉴频鉴相器重通路径上的延时,主要也是为了消除鉴频鉴相器的死区问题引入的。经过一个周期后,最终流入到环路滤波器上的电荷量用 $\int (I_{UP}-I_{DN})$ 来表示。电荷泵上下电流的总电荷  $Q_{UP}$  和  $Q_{UP}$  的表达式如下

$$Q_{dn} = I_{UP} \left[ \phi + t_{d} + \left( t_{f,up} - t_{r,up} \right) / 2 \right] + I_{I,up} \left( T_{ref} - \phi \right)$$

(3.5)

$$Q_{dn} = I_{DN} \left[ t_d + \left( t_{f,dn} - t_{r,dn} \right) / 2 \right] + I_{I,dn} \left( T_{ref} - \phi \right)$$

(3.6)

其中, $I_{l,up}$  和  $I_{l,dn}$  分别是上下开关的泄露电流。于是,可以得到流入环路滤波器的总电荷的表达式

$$Q_{tot} = Q_{up} - Q_{dn}$$

$$= I_{CP} \Phi + \frac{\Delta I_{CP}}{2} \Phi + \Delta I_{CP} t_d + \frac{I_{CP}}{2} \left[ \left( t_{f,up} - t_{f,dn} \right) + \left( t_{r,dn} - t_{r,up} \right) \right]$$

$$+ \frac{I_{CP}}{4} \left[ \left( t_{f,up} - t_{f,up} \right) + \left( t_{r,dn} - t_{r,dn} \right) \right] + \Delta I_{I} \left( T_{ref} - \Phi \right)$$

(3.7)

其中, $\Delta I_{CP} = I_{UP} - I_{DN}$ 是由电荷泵上下电流源不匹配造成的静态误差; $I_{CP}$ 是上下

电流的平均值( $I_{UP}$ - $I_{DN}$ )/2; $\Delta I_1 = I_{I,up}$ - $I_{I,dn}$ 表示的是上下电流源各自开关的泄漏电流之间的不匹配。上式中的第一项  $I_{CP}$ · $\Phi$  是希望得到的线性部分。第二项的非线性来自电荷泵上下电流源的不匹配。后面几项表示的非线性相对比较固定。同时,可以看出,鉴频鉴相器检测到的相位差  $\Phi$  越小,传输特性表现的非线性就越明显。

基于图 3-9 的时序分析,可以得到鉴频鉴相器和电荷泵的传输特性函数,一般把 **Q**tot 用多项式来表示

$$Q_{tot} = a_0 + a_1 \cdot x + a_2 \cdot x^2 + a_3 \cdot x^3$$

(3.8)

其中x经过归一化处理,表示相位误差与相位误差的标准差 $\sigma(\phi)$ 之间的比值

$$x = \frac{\Phi}{\sigma(\Phi)} \tag{3.9}$$

多项式的系数可以依据鉴频鉴相器和电荷泵的非线性特性近似得到,从公式 (3.8)我们可以得到系数 a<sub>0</sub>

$$a_{0} \approx \frac{\Delta I_{CP}}{2} \Phi + \Delta I_{CP} t_{d} + \frac{I_{CP}}{2} \left[ \left( t_{f,up} - t_{f,dn} \right) + \left( t_{r,dn} - t_{r,up} \right) \right] + \frac{I_{CP}}{4} \left[ \left( t_{f,up} - t_{f,up} \right) + \left( t_{r,dn} - t_{r,dn} \right) \right] + \Delta I_{I} \left( T_{ref} - \Phi \right)$$

(3.10)

鉴频鉴相器输出端的相位误差由多模预分频器的分数部分决定。考虑到之前 所述的事实,鉴频鉴相器和电荷泵的线性部分传输函数可以近似的表示为

$$\frac{a_1}{\sigma(\Phi)} \approx N_{frac} I_{CP} \cdot \left(1 - \frac{\Delta I_{CP}}{I_{CP}}\right)$$

(3.11)

其中, $N_{frac}$ 表示控制分频器分频比中的分数部分。同样的方式也可以用来估计更高阶系数  $a_1$  和  $a_2$ 。

另外一个非线性来自环路中的分频器。由于信号经过分频处理的延时受 **ΔΣ** 调制器输出的数据流控制,所以也会引起带外的高频量化噪声折叠回带内,增加带内的相位噪声和频率综合器输出端的毛刺成分。

需要说明的是, $\Delta\Sigma$  分数分频频率综合器在环路锁定之后,实现的是一种动态的锁定。所以鉴频鉴相器检测到的相位差也是在不停地抖动。经过反馈回路的调制,实际上, $\Delta\Sigma$  分数分频频率综合器有一个永远没法消除的非线性特性。

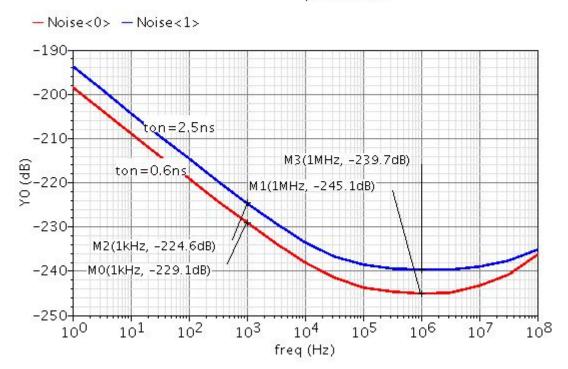

#### 3.3.4 导通时间

为了消除死区效应,设计中特地在重置回路中添加延迟单元。所以即使在环路锁定的情况下,电荷泵也会存在一个  $t_{on}$  的导通时间。此时便可以直观地认识到,鉴频鉴相器的噪声也就是在这个  $t_{on}$  的导通时间内,通过电荷泵的电流噪声作用到整个环路中。电荷泵的电流噪声在不同导通时间下的仿真结果如图 3-10 所示。

#### phase noise

图 3-10 不同导通时间下的电流噪声仿真结果

在 3.3.2 小节中,已经介绍了由 Cranincks 提出的噪声模型。为了方便回忆, 再次引用该相噪模型的表达式

$$\ell\left\{\Delta\omega\ll\omega_{c}\right\} = \frac{1}{2}\cdot\left(2\cdot\pi\cdot\frac{N}{I_{cp}}\right)^{2}\cdot2\cdot\alpha_{cp}\cdot4\cdot k\cdot T\cdot\frac{2\cdot I_{cp}}{\left(V_{GS}-V_{t}\right)_{cp}}$$

(3.12)

其中,  $\alpha_{cp}$  表示电荷泵的导通时间在一个周期中占的时间比  $t_{cn}/T$ 。这里的时钟周期 T 由参考时钟决定。如果参考时钟的频率不变,那么导通时间越大,鉴频鉴相器贡献的噪声也就越大。

在电路的设计中,应尽量选择较小的导通时间。但是受电荷泵开关速率的限制,过小的导通时间,会使得电荷泵不能正常开启。这也就回到了之前讨论的死区效应问题。

# 3.4 鉴频鉴相器电路设计

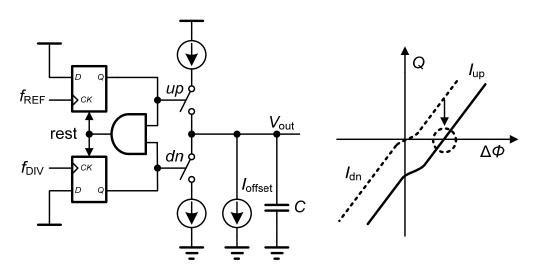

### 3.4.1 降低非线性技术

前面已经讨论过鉴频鉴相器和电荷泵电路产生的非线性。由于在环路锁定的时候,电路主要工作在相位差为零的附近区域,而这一区域的非线性恰恰是最严重的。通过观察,我们发现电荷泵上下电流的不匹配是引起电路非线性的主要原因[33]。所以,很多降低非线的方法也围绕电荷泵上下电流的不匹配而展开。

在文献[34]中,作者通过在电荷泵中添加了一个直流偏移电流源,使得鉴频

鉴相器和电荷泵的传输特性曲线整体下移,如图 3-11 所示。这样就减小了在过零点的非线性,但是引入的电流源也会注入额外的噪声到环路滤波器中,甚至可能改变环路的传输特性。在文献[20]中,作者通过运用复制支路和可控的偏置电流源来补偿电荷泵上下电流的不匹配,来达到减小非线性的目的。但是该种方法使得电荷泵的设计变得很复杂。

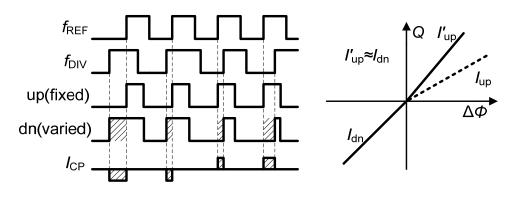

图 3-11 添加直流偏置电流源电路

本论文采用一种比较方便的技术来降低非线性。不同于前面两种方法,本论文从鉴频鉴相器的结构入手,通过改变两个 D 触发器的复位信号,来使得电荷泵的上下电流更加匹配。观察图 3-12 的波形,up 开关信号的脉冲宽度不随相位差的变化而变化,只有 dn 开关信号的脉冲宽度才随着相位差的变化而变化。也就说在电荷泵的上下电流中只有放电电流在变化, $I'_{up} \approx I_{dn}$ 。此时,上下电流的匹配问题主要受放电电流的影响,如图 3-12(b)所示。

图 3-12 PFD/CP 的线性化

接下来,我们通过设计鉴频鉴相器来实现上述功能。为了比较该种技术与传统模式的鉴频鉴相器的性能差别,在设计中保留了传统的工作模式。而且考虑到不同导通时间对鉴频鉴相器的影响,在设计中还引入了可供选择导通时间的功能。所以实际的鉴频鉴相器电路比较复杂。

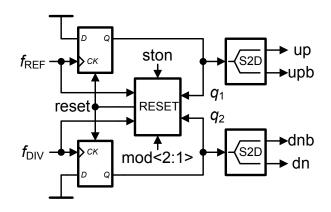

### 3.4.2 鉴频鉴相器电路

图 3-13 PFD 具体电路

图 3-13 是具体的鉴频鉴相器电路。其中,单端转双端电路(Single to Doubler, S2D) 采用了交叉耦合的反相器得到互补的开关信号,具体电路如图 3-7 所示。 RESET 模块代替了简单的逻辑与门电路,但同样是为了产生两个 D 触发器的复位信号,只是内部电路更为复杂。信号 mod<2:1>可以切换两种工作模式: 一种是传统的鉴频鉴相器的工作模式,另一种是降低非线性而采用的工作模式。信号 ston 用于控制第一种工作模式中的延迟时间,也就是鉴频鉴相器的导通时间。

图 3-14 是 RESET 模块内的具体电路。其中还用到了三个延迟单元,它们的值都选取为 $\tau_{cl}$ =2.5ns; 四个二选一选择器,由数字信号 mod<2:1>和 ston 控制。

图 3-14 RESET 模块的具体电路

上行通路中的两个输入信号  $q_1$  和  $q_2$ ,分别来自图 3-13 两个 D 触发器的输出端,经过逻辑与门的作用产生复位信号。该复位信号在达到第一个选择器之前,被分为两路。其中一路经过延迟单元,使得复位信号滞后 $\tau_d$ 时间。

下行通路中的电路结构类似与一个简单的鉴频鉴相器,如图 3-14。它的工作原理也类似简单的鉴频鉴相器电路,不同的是输入信号  $f_{REF}$  和  $f_{DIV}$  经过延迟单

元处理,并且逻辑与门被替换成一个选择器。该电路的主要目的是得到一个固定脉宽的有效导通信号,例如 3.4.1 小节提到的 up 信号。然后由下行通路中第二个选择器决定:选择以参考时钟信号还是以分频器输出信号作为固定信号。

最后一个选择器则决定了是选择上行通路还是下行通路,也就是两种工作模式的选取。

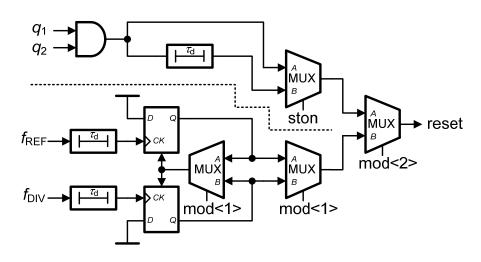

### 3.4.3 Lock Detector 电路

图 3-15 是一个环路锁定检测电路。它由两个上升沿触发的 D 触发器、两个延迟单元和一个逻辑与门构成,主要用于检测电路是否正常锁定。其工作原理是:当分频器输出信号  $f_{DIV}$  波形的上升沿在经过一个  $\tau_{CI}$  的延时后,D1 触发器被触发。此时,参考时钟信号  $f_{REF}$  便被复制到输出端口 Q1。同理,当参考时钟信号  $f_{REF}$  波形的上升沿在经过  $\tau_{CI}$  的延时后,D2 触发器被触发。分频器输出信号  $f_{DIV}$  便被复制到输出端口 Q2。如果与非门检测到两个输入信号 Q1 和 Q2 都为高电平,即参考时钟信号  $f_{REF}$  和分频器输出信号  $f_{DIV}$  在  $\tau_{CI}$  时间内都为高电平,则在辑与门的输出信号显示为高电平,表示锁相环正常锁定。

在芯片的测试过程中,可以通过该电路判断电路是否正常锁定。另一方面, 考虑到环路的锁定速度和噪声性能间的折中,我们需要通过该电路来确认电路的 锁定情况,然后通过环路控制电路自动进行模式间的切换。

图 3-15 Lock Detector 电路

#### 3.4.4 鉴频鉴相器版图

在版图规划时,需要特别注意数字电路与模拟电路之间的隔离问题。本设计就把鉴频鉴相器置于深井中。横跨在版图上方的两条第五铝导线是电源地。在空间允许的情况下,应尽量把电源地线设计的宽些,以减小电源地线的电阻。

图 3-16 PFD 版图

## 3.4.5 工作模式

表 3-1 对鉴频鉴相器的工作模式做了总结。在传统工作模式下,导通时间由 ston 信号选择,分别为 0.6ns 和 2.5ns。在降低电路非线性的工作模式下,可由 mode 信号选择以充电电流开关 up 为固定脉宽信号或者放电电流开关 dn 为固定脉宽信号。

控制信号

工作模式

mode=0x

ston=00 ton=0.6ns (传统)

ston=11 ton=2.5ns (传统)

mode=10 ston=xx up 信号固定, dn 信号变动 (线性化)

mode=11 ston=xx dn 信号固定, up 信号变动 (线性化)

表 3-1 鉴频鉴相器的工作模式

# 3.5 本章小结

- 1) 介绍了鉴频鉴相器的几种电路结构,重点介绍了基于电荷泵型的鉴频鉴相器:

- 2) 具体分析了鉴频鉴相器中的一些非理想效应,并且给出了相应的解决方案;

- 3) 介绍了鉴频鉴相器的两个噪声模型,对于设计电路具有指导意义;

- **4)** 详细分析了鉴频鉴相器和电荷泵电路中的非线性特性,并且提出了一种降低 非线性的改进技术;

- 5) 最后给出了鉴频鉴相器的具体电路并对各种工作模式做了总结;

# 第四章 全差分电荷泵分析与设计

# 4.1 引言

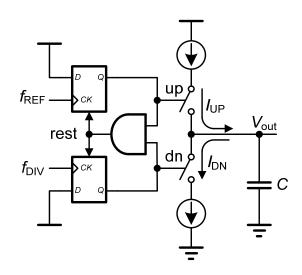

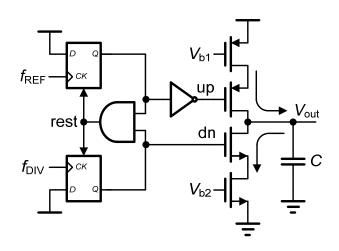

电荷泵锁相环由于其锁定时间短、线性范围大等优势,是目前应用最广的锁相环。在锁相环中引入电荷泵,实际上并没有改变锁相环的工作原理。它的主要贡献在于优化了相位差到压控电压的转变过程。通过电荷泵电流 Icp 的灵活设计,可以方便地控制环路的各种性能。但就其本质而言,电荷泵锁相环仍就是一个离散采样的系统[11],所以需要考虑一些周期性的非理想特性。电荷泵按输出方式主要分为两类,单端输出和差分输出。本文采用全差分的电荷泵设计,用一个共模反馈电路来提高电路的稳定性[21]。同时环路滤波器也采用全差分结构,在设计中尽量减少电流不匹配等效应的影响。

# 4.2 全差分电荷泵

在频率综合器中,电荷泵主要完成了把数字脉冲信号到模拟信号的转换过程。如果鉴频鉴相器和电荷泵都是完全理想的线性模型,就不会存在静态相位误差等情况。但实际上,电荷泵在设计中需要考虑很多非理想因素,包括电流不匹配,漏电流,电荷共享等。电荷泵性能的好坏,直接决定了引起参考毛刺的水平(这已在第二章讨论过)。因此,在电荷泵的设计过程中要尽量考虑这些因素。

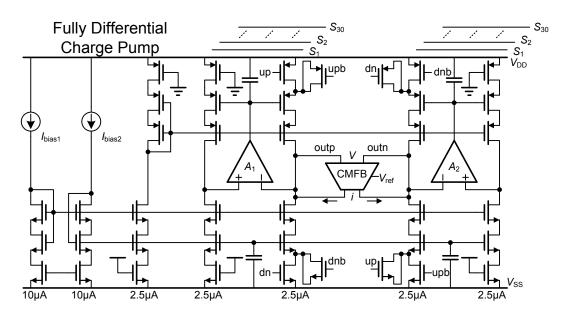

为了采用合适的电荷泵结构,需要比较不同结构之间的性能。文献[22]已经在这个方面做了很多工作。本论文采用全差分结构的电荷泵电路,如图 4-1 所示。

图 4-1 全差分电荷泵的框架图

由于电荷泵的全差分结构,鉴频鉴相器需要产生两组互补的开关信号分别控制全差分电荷泵的两路上下开关。环路滤波器也被设计成差分的,有两个无源三阶滤波器构成。在本设计中,考虑到滤波器的差分特性,把滤波器中的两个大电容  $C_1$ 用一个电容值为  $C_1$ /2 的电容代替,如图所示。这一简化不但没有改变滤波器的传递函数,而且使得电容的面积减小,大大节省了芯片的面积[23]。

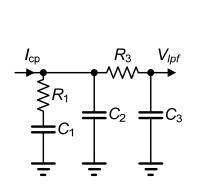

我们从无源三阶滤波器出发,来考察环路的稳定特性,其结构如图 4-2(a) 所示。电荷泵电流源  $I_{cp}$  和电容  $C_1$  构成了一个积分器电路。电阻  $R_1$  引入了一个零点来提高环路的相位裕度,改善了环路的瞬态响应。但是,在电荷泵导通关断的瞬间,它会引起压控电压处一个大小为  $I_{cp}R$  的波纹。这个波纹经过压控振荡器作用便会在输出产生多余的抖动。为了压制这个波纹,引入了一个相对较小的电容  $C_2$ ,但同时也引入第二个极点。此时,滤波器还只是二阶的,加入  $R_3$  和  $C_3$  使得滤波器变为三阶。由于压控振荡器在原点处也贡献一个极点,所以三阶无源滤波器所在环路实际上是一个四阶环路。利用相位裕度最大法的方法[24],从开环传递函数的波特图着手,来研究环路的稳定特性。四阶环路的开环传递函数的波特图,如图 4-2(b)所示。其中, $\omega_p$ 表示环路的极点, $\omega_z$ 表示环路的零点, $\omega_c$ 表示开环环路的带宽。较高的阶数使得带宽变得更加陡峭,但是也可以看出,较高的阶数会存在稳定性问题。所以一般环路不会采用更高阶数的滤波器。

(a) 三阶无源滤波器

(b) 四阶开环传递函数波特图

图 4-2 三阶无源滤波器及其开环环路的波特图

在工艺的实现中,考虑到无源滤波器电阻和电容精度的要求。我们分别采用高阻的多晶硅电阻(Rphpoly)和金属电容(MIM)来设计,因为它们随工艺电压以及温度的变化相对较小。

全差分电荷泵相对于传统的单端电荷泵有几个比较明显的优势[22]:

a) 全差分电荷泵的电压输出范围增大了一倍,不仅提高了电荷泵的线性度, 而且可以减小压控振荡器的增益 *K*<sub>vco</sub>,这个对于单端电荷泵本来就有限的 电压输出范围来说,是一个巨大的优势;

- b) 全差分的输出端对于电荷泵的泄露电流显得不那么敏感了,从而减小了参 考毛刺,因为泄露电流可以看成一种共模失配,而全差分的结构恰恰可以 抵消共模误差;

- c) 全差分电荷泵对电源地以及来自衬底的噪声有很好的抑制能力。

需要注意的是,全差分结构滤波器相当于两个单端滤波器并联,其产生的电阻噪声也就是单端的两倍。

# 4.3 设计考虑

在电荷泵的设计中,最理想的情况是:上下两路电流完全匹配;对来自鉴频 鉴相器检测到的相位差,能够快速准确地响应;具有完全线性的传输特性;开关 导通关断的瞬间,不会影响环路滤波器上的压控电压。但在实际的电路中,器件 的功能实现本身就是近似的,我们只能通过减小电路中的一些非理想因素,来改善性能。

### 4.3.1 晶体管尺寸的选择

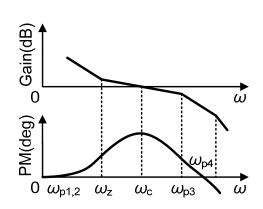

图 4-3 左侧是本设计中采用的全差分电荷泵的一部分。其中右边支路由 M1~M6 构成电荷泵的输出通路,左边支路主要是为了提高上下电流匹配而引入 的复制通路。M1 和 M6 作为电荷泵通路的开关,它的尺寸设计至关重要。可以 把它们看成开关采样电路来加以分析,如图右侧所示。其中 C<sub>H</sub> 是采样电容,它 的速度主要取决于两个因素: 开关的导通电阻以及采样电容的大小[25]。

图 4-3 单端输出电荷泵及开关电容模型

因此,想要提高开关速率,我们只能通过增大开关管的宽长比 W/L 来减小

沟道电阻,或者减小采样电容  $C_H$ 。沟道电阻的大小与迁移率  $\mu$  成反比,由于 PMOS 管和 NMOS 管的类型不同,它们的迁移率差别很大(在 TSMC 的 0.18um 工艺下,  $\mu_n \approx 6\mu_n$ )。所以在同样的尺寸下,NMOS 管沟道电阻更小,速度更快, 在设计时要考虑到这一点。另外,我们可以看到图 4-3 中的源端开关 M1 和 M6, 实际上,它们的工作区域只在截止区和线性区之间切换;而输出端附近的共源共 栅管 M2~M5, 它们的工作区域在截止区与饱和区之间切换。所以在开关工作的 时候,我们还需考虑到 M2~M6 管贡献的沟道电阻。它们的尺寸大小也影响着上 下开关的速率。公式(4.1)和公式(4.2)分别表示线性区和饱和区的沟道电阻,其 中  $\mu$  表示电子或者空穴的迁移率, $C_{\rm ox}$  表示单位面积的栅氧化层电容, $V_{\rm os}$  表示 栅源电压, $V_t$ 是晶体管的阈值电压, $\Lambda$ 是沟道调制系数,

$$R_{on,triode} = \frac{1}{\mu \cdot C_{ox} \cdot \frac{W}{I} \cdot (V_{gs} - V_{t})}$$

(4.1)

$$R_{on,triode} = \frac{1}{\mu \cdot C_{ox} \cdot \frac{W}{L} \cdot (V_{gs} - V_{t})}$$

$$R_{on,sat} = \frac{1}{\frac{\lambda \cdot \mu \cdot C_{ox} \cdot W}{2L} \cdot (V_{gs} - V_{t})^{2}}$$

$$(4.1)$$

根据前面的讨论,我们来介绍下具体管子尺寸的选取。首先,选择两个开关 管 M1、M6 的尺寸。在本设计中,我们采用最小的沟道长度以保证在  $t_{con}$  导通内 能够快速响应开关信号, 选取(W/L)<sub>M1.M6</sub>=2µm /0.18µm; 然后,选取共源共栅 管 M2~M5 的尺寸。考虑到 NMOS 管的速率快于 PMOS 管,为了使上下两路电 路的速率一样,我们在选择 PMOS 管的尺寸上要大于 NMOS 管。这里取  $(W/L)_{M2}$ =0.6 $\mu$ m /0.6 $\mu$ m, $(W/L)_{M3}$ =0.8 $\mu$ m /0.2 $\mu$ m, $(W/L)_{M4}$ =0.4 $\mu$ m /0.5 $\mu$ m 以及  $(W/L)_{M5}$ =0.25 $\mu$ m /1.6 $\mu$ m。最后,需要注意的是,由于管子的寄生电容,在增大 管子尺寸来减小沟道电阻的同时,也增大了寄生电容的值。它会部分抵消增大宽 长比的贡献,而使速度减缓。所以我们经常要考虑两者同时作用,选择合适的宽 长比 W/L, 使得上下两路电流速度一样。

### 4.3.2 非理想因素及解决方案

电荷泵的非理想因素有很多,包括漏电流,衬底耦合,时钟馈通,沟道电荷 注入, 电荷共享以及上下电流不匹配等。下面简单的阐述这些非理想因素, 并且 给出相应的解决方案。

- 1)漏电流。随着工艺的进步,栅氧化层越来越薄,使得栅到源漏以及衬底的漏 电流越来越大。但是由于全差分电荷泵的结构优势,漏电流的影响可以忽略;

- 2) 衬底耦合。衬底存在很多的噪声和干扰,有来自数字电路的,也有来自射频 振荡器耦合的。但是全差分的结构对其抑制得还是很好的。本设计还引入了 另外两个措施:一是,在版图的设计中,把器件安置在深井里。由于深井隔 离衬底,具有很好抗干扰能力。二是,分别对数字电路、模拟电路和射频电

路来采用不同的电源地,并且采用低压差线性稳压器(Low Dropout Regulator, LDO)电路对电源地进行稳压处理;

- 3) 时钟馈通。由于开关管的栅漏电容,开关信号的波动也会被耦合到输出端。 本设计在源端开关和输出端之间加入一对共源共栅管,如图 4-4 中虚线框所 示,提高输出阻抗的同时也起到了很好的隔离作用;

- 4) 电荷注入。在开关管关断的瞬间,积累在沟道里的电荷会进入到环路滤波器中,使得压控电压变化。本设计在开关管的漏端放置了一个额外的管子,如图 4-4 中虚线圈所示。其大小为开关管的一半,由互补的开关信号控制,可以吸收和释放由于电荷注入效应引起的波动。

图 4-4 单端输出电荷泵及开关电容模型

#### 4.3.3 管子间 mismatch 的影响

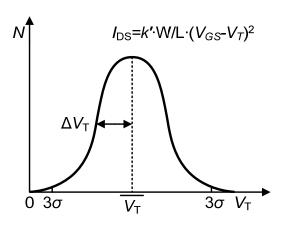

在模拟电路的设计中,除了上述非理想因素的影响,其实有一个更为重要的因素需要考虑。那就是管子间的匹配问题[26]。由于制造过程中每一道工艺的不确定性,即便参数尺寸都相同的管子间都会存在随机的不匹配。沟道和栅极的掺杂程度决定了管子的阈值电压  $V_T$ ;光刻和掩膜决定了管子宽长 W/L 的不匹配等。实际上,随着沟道长度的减小,管之间的不匹配程度变大。它会引起电路的直流失调、有限偶次失真和更低的共模抑制等现象,从而严重影响电路的性能[14]。

我们先以晶体管的阈值电压为例,如图 **4-5** 所示。管子数 N 与实际阈值电压  $V_T$  的分布图。通常,它们的统计也表现高斯分布,大约只有 **0.5%**的管子会偏离平均值的  $3\sigma$  以外( $\sigma$  为标准差)。在电路设计中,往往会把设计的指标定在这

个范围内,我们可以通过 Mont Carlo 分析,以直方图的形式来观察这个范围。

图 4-5 晶体管阈值电压的随机不匹配

很多模型表明阈值电压偏离的标准差与晶体管的面积的平方根成反比,如下 式所示

$$\sigma_{\Delta V} = \frac{A_{V}}{\sqrt{WL}} \tag{4.3}$$

其中  $A_{\rm V}$ 表示与工艺技术有关的系数。随着尺寸 L 的减小,栅氧化层的厚度也随之减小, $N_{\rm B}$ 表示衬底的掺杂浓度

$$A_{V} \sim t_{OX} \sqrt[4]{N_{B}} \tag{4.4}$$

同样的,晶体管的宽长比也存在随机的不匹配。其中  $A_{WL}$  表示晶体管尺寸的不匹配系数,它跟掩膜和光刻等工艺技术有关,而且是一个比  $A_{V}$  大的值

$$\frac{\Delta W/L}{\overline{W/L}} = A_{WL} \sqrt{\frac{1}{W^2} + \frac{1}{L^2}} \tag{4.5}$$

随着最小尺寸 L 逐渐减小,不过始终会有一个约为 2%的偏差。尽管上述的阈值失配系数  $A_V$  会越来越小,但是晶体管的宽长比系数  $A_{WL}$  却趋于一个常数。因此管子尺寸的不匹配对电路性能的影响也就显得越来越重要。

从上面的分析可以看出,在电路的设计中,如果想减小不匹配的程度,只能通过增大晶体管的面积 WL 来实现。随着晶体管面积 WL 的增大,随机变化经历更大的"求平均"过程。如果把晶体管看成许多小的晶体管的并联,那么对于宽度为 W<sub>0</sub> 的管子,它的等效长度  $L_{eq} \approx (L_1 + L_2 + \cdots + L_n)/n$ 。随着 n 的增大,等效沟道长度  $\Delta L_{eq}$  的变化也将减小,如公式(4.6)所示。其中, $\Delta L_0$  是一个管子长度 L 变化的统计量

$$\Delta L_{eq} \approx \frac{\left(\Delta L_1^2 + \Delta L_2^2 + \dots + \Delta L_n^2\right)^{1/2}}{n} = \frac{\left(n\Delta L_0^2\right)^{1/2}}{n} = \frac{\Delta L_0}{\sqrt{n}}$$

(4.6)

接下来,考察晶体管间这些随机的不匹配对电流镜的影响。在电荷泵的设计

中用到了很多处电流镜,如图 4-6 中虚线框所示。输出电流因晶体管不匹配而产生的误差,有如下关系

$$\frac{\Delta I_{out}}{\overline{I_{out}}} = \frac{\Delta V_T}{\left(V_{GS} - V_T\right)/2} + \frac{\Delta K'}{\overline{K}} + \frac{\Delta W/L}{\overline{W/L}}$$

(4.7)

其中  $\Delta K'$ 同上面讨论的阈值和宽长度一样,也是工艺随机不匹配的一个表现。

图 4-6 全差分电荷泵支路电流源的不匹配

通常,为了提高上下电流的匹配,电荷泵的设计中往往会引入复制通路。其原理就是利用电流镜,使得上下电流都去参考复制通路的电流从而达到匹配的目的。即便有运放使得电荷泵通路与复制通路匹配的更好,但是电流源管子间随机的不匹配是没法消除的。为了使 M2~M5 和 M10~M13 能够匹配的更好,需要有目的增加电流源管子的尺寸,以及增大它们的过驱动电压(V<sub>GS</sub>-V<sub>T</sub>)。但是电流源管的尺寸取得太大,则会增加开关到输出端的阻抗,并且产生较大的寄生电容。这又会影响开关速率。所以管子尺寸的选取是个折中的过程。

## 4.3.4 电荷泵电流的影响

在频率综合器中,电荷泵的大小跟环路的带宽有直接的关系。于是,我们先来推到环路带宽的表达式。在 2.4.1 章节中,通过对整数分频频率综合器的环路建模得到了开环传递函数

$$G(s) = \frac{I_{cp} \cdot Z_{lpf}(s) \cdot K_{vco}}{2\pi \cdot s}$$

(4.8)

为了得到无源三阶滤波器的传递函数,可以参考图 4-1,推导并且整理得到

$$Z_{lpf}(s) = \left(R_{1}C_{1} + \frac{1}{s}\right)$$

$$\cdot \frac{1}{R_{1}R_{3}C_{1}C_{2}C_{3}s^{2} + \left[R_{1}C_{1}(C_{2} + C_{3}) + R_{3}C_{3}(C_{1} + C_{2})\right]s + C_{1} + C_{2} + C_{3}}$$

(4.9)

采用近似环路带宽的概念[2],得到四阶环路的近似环路带宽 $\omega_{c}$

$$\omega_c = \frac{I_{cp} K_{vco} R_1}{2\pi N} \frac{C_1}{C_1 + C_2 + C_3}$$

(4.10)

从上式可以看出,如果分频比 N 和压控振荡器的调谐系数  $K_{vco}$  发生变化,那么环路的带宽也会改变。所以为了使环路带宽相对稳定,在分频比 N 发生变化的同时,需要相应地控制电荷泵电流的大小。

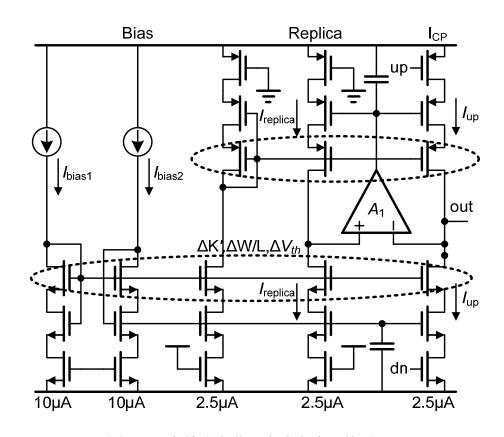

在本设计中,全差分电荷泵的电流被设计成  $5\mu A$ ,每条支路分别为  $2.5\mu A$ ,而这样的全差分电荷泵单元有 30 个,其中有 15 个是相对固定的,另外 15 个全差分电荷泵单元由 4bit 信号控制开启和导通,使得  $I_{cp}/N$  的比值基本保持不变,所以总的电荷泵电流  $I_{cp}$ 为  $75~150\mu A$ 。

另外,环路的带宽也决定了锁相环的建立时间,也就是说电荷泵电流的大小也跟环路的建立时间有关。在章节 2.4.3 给出了建立时间与电荷泵电流大小的关系式(2.13)。所以如果想改变环路的建立时间,可以通过 /cp 这个量来调节。

最后,从环路的表达式可以看出,电荷泵电流还可以通过影响系统中零极点的分布来影响环路的稳定性。

# 4.4 电荷泵电路设计

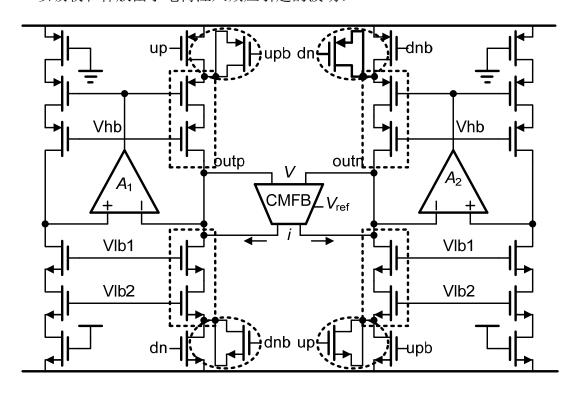

# 4.4.1 全差分电路

图 4-7 是全差分电荷泵的电路图。左边部分引入了来自带隙基准(BandGap) 提供的两路大小为  $10\mu$ A 的电流。经过电流镜的复制得到一系列大小为  $2.5\mu$ A 的电流支路。然后通过 Wide-Swing 电路对电荷泵上下电流源 Cascode 进行偏置。右边部分为全差分电荷泵的核心电路,由两个完全对称的单端电荷泵电路以及一个共模反馈电路(Common Mode Feedback, CMFB)组成。实际上,全差分电荷泵两边类似的单端电荷泵各有 30 个,如下图所注  $S_1 \sim S_{30}$ 。它们的输出端都接在端口 outp 或端口 outn,并且共用一共模反馈电路。其中  $S_1 \sim S_{15}$  在电荷泵工作时一直正常工作,而  $S_{16} \sim S_{30}$  是可选的,根据分频比的变化选择开启。

在每个单端电荷泵的设计中,为了使上下电流能更好的匹配,引入了复制通路。但是它们分别共用运放 A1 和 A2 来钳位输出端电压和复制通路电压,通过

这种方式来减小由于沟道调制效应的电流差异。在电荷泵电流源的栅端分别用 MOS 电容,来稳定电压[22]。因为源端开关的信号往往会通过耦合馈通等效应 使得靠近开关的电流源栅端电压发生明显的波动。在开关管的漏端,分别引入了 悬置的 MOS 电容,它们的尺寸设计为相应开关管子的一半,用于吸收和释放由于开关变化瞬间的注入电荷,所以它们的控制信号也是相应开关管子的互补信号。

图 4-7 全差分电荷泵电路

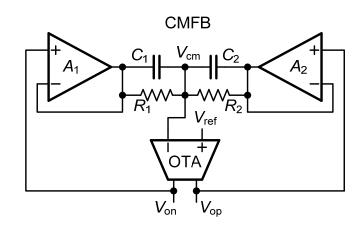

### 4.4.2 CMFB 电路

为了使得全差分电荷泵输出端的共模电压不发生偏移,提高电荷泵的对称特性,通常会引入共模反馈电路,如图 4-8 所示。

图 4-8 共模反馈电路

其工作原理,就是通过电容电阻采样网络来得到全差分电荷泵两个输出端口的共模电压  $V_{cm}=(V_{op}+V_{on})/2$ ,然后与期望的共模电压  $V_{ref}$  比较。为了不影响电

荷泵的输出端,分别有缓冲放大器 A1 和 A2 对它们进行采样。如果  $V_{cm}$  不等于  $V_{ref}$ ,跨导放大器(Operational Transconductance Amplifier, OTA)便会对电荷泵 注入或者抽取电流。通过负反馈的作用使得  $V_{cm}$ 等于  $V_{ref}$ 。需要注意的是,在设计跨导放大器的时候,应当考虑其噪声对环路的贡献。因此,在跨到放大器最后一级的设计中,我们采用较小的电流来控制电流噪声的贡献,并且选择大尺寸的管子来减小 1/f 噪声的贡献。

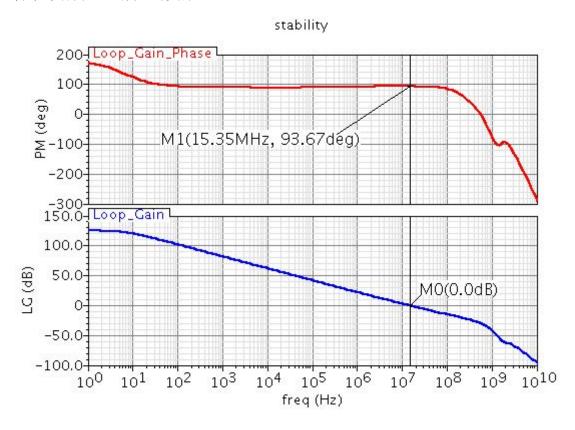

图 4-9 CMFB 电路的瞬态特性

为了保证共模反馈电路在整个环路中能够正常工作,它的带宽必须设计的足够小(一般相比环路带宽小两个数量级比较合适)。在电路中需要独立于环路滤波器进行仿真,得到其瞬态特性的仿真结果,如图 **4-9** 所示。

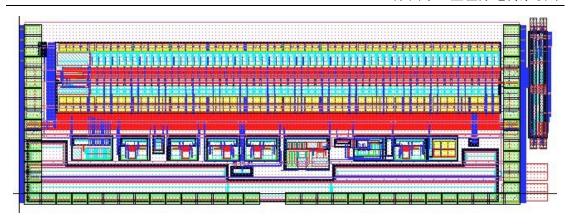

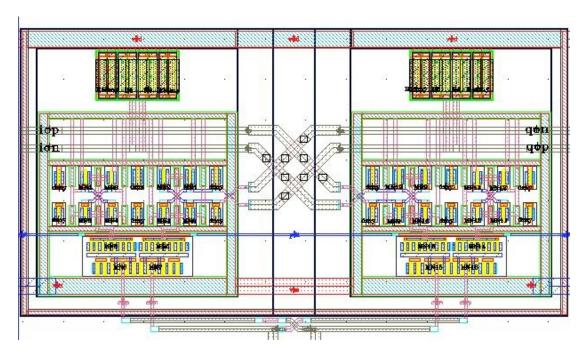

#### 4.4.3 电荷泵版图

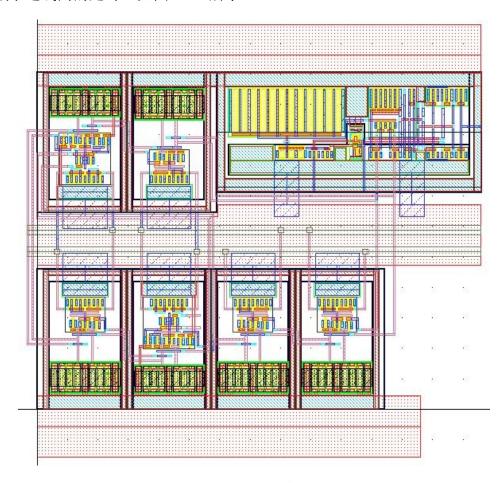

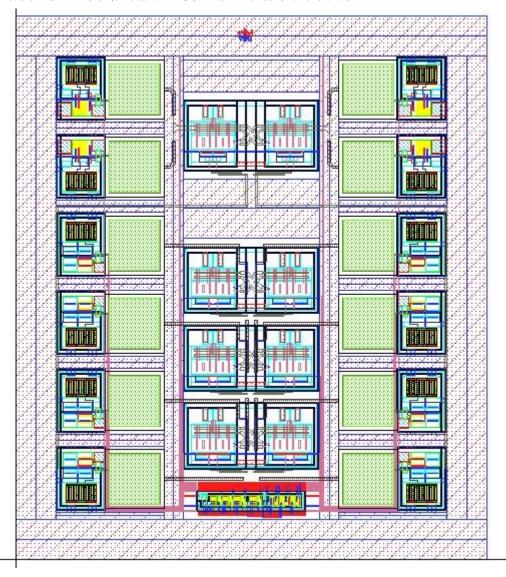

全差分电荷泵电路对对称性的要求比较高。考虑到相邻支路的工艺误差波动相对较小,所以选择以全差分电荷泵而不是以单端支路为单元规划版图。这样的单元有 30 个,它们以队列的形式分布,如图 4-10 所示。在电荷泵阵列的下方,是一些辅助的电路模块,包括电流源、钳位电压的运算放大器,共模反馈电路等等。外围呈现了绿色的部分是两级运放中用到的 MIM 电容。最右侧是上一章介绍的鉴频鉴相器的版图。

图 4-10 电荷泵版图

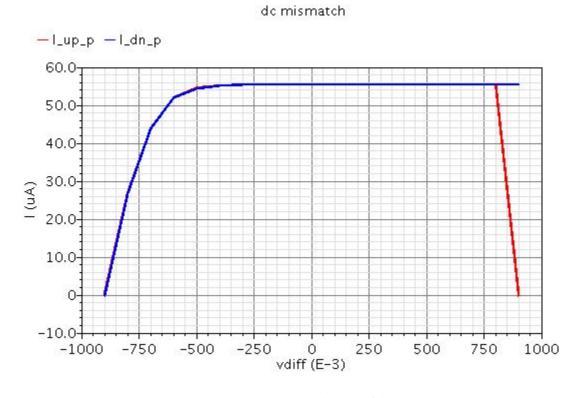

### 4.4.4 仿真结果

在电荷泵的设计中,我们最关心的是上下电流的匹配,其中包括静态电流匹配和动态电流匹配。图 4-11 是全差分电荷泵直流匹配的仿真曲线,在输出节点电压偏移-0.5V~0.5V 范围内,上下支路的电流的偏差控制在千分之一的误差内。

图 4-11 电荷泵直流匹配特性

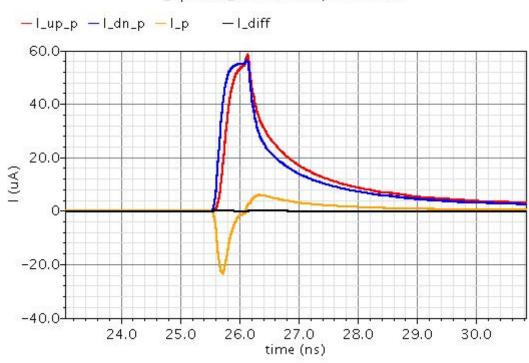

针对电荷泵动态电流匹配中的毛刺,利用全差分结构的电荷泵可以很好的解决这一问题,如仿真图 4-12 所示。黄色曲线表示了单路电荷泵中上下电流的差异,黑色曲线表示左右两路电荷泵的差异抵消以后的结果,从中也可以看到全差分电荷泵电路所具有的优势。

I\_up and I\_dn mismatch, ton=0.6ns

图 4-12 电荷泵动态匹配性能

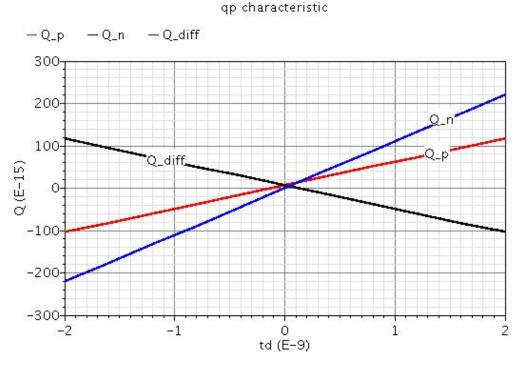

通过仿真电荷泵流入环路滤波器的电荷量随相位误差的变化,我们得到图 4-13。其中 Q\_p 表示全差分电荷泵左边支路流入环路滤波器的电荷量; Q\_n 表示右边支路流入的电荷量; Q\_diff 表示全差分电荷泵流入环路滤波器的电荷量。

图 4-13 电荷泵 qp 特性

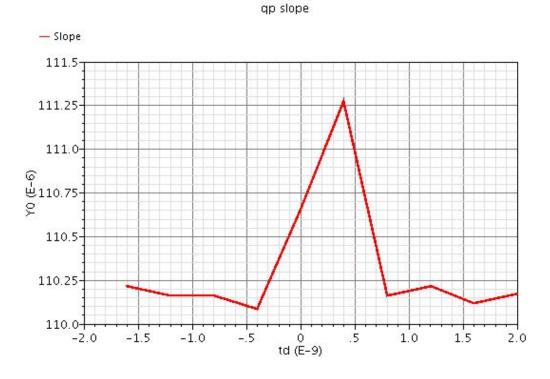

图 4-14 是 Q\_diff 的斜率,可以看到在相位差为零附近,电荷泵的非线性表现的比较明显,但是仍能控制在很小的误差内。

图 4-14 电荷泵 qp 曲线斜率

# 4.5 本章小结

- 1) 介绍了全差分结构对整个环路结构的影响,包括需要相应设计鉴频鉴相器电路以及环路滤波器电路。顺便分析了环路滤波器的参数对整个环路特性的影响,总结了全差分结构的电荷泵的优势;

- 2) 介绍了在电荷泵设计中的细节问题,包括电荷泵管子尺寸的选取,一些非理想因素的考虑;

- 3) 在电路设计中,特别分析了管子间的非线性。它对电荷泵性能的影响是起决定性的。并且提出了改善的方法:

- 4) 分析了电荷泵电流大小对整个频率综合器性能的影响;

- 5) 给出了全差分电荷泵的仿真结果,包括电荷泵上下电流的静态匹配和动态匹配。同时也仿真了共模反馈电路的稳定特性;

# 第五章 分频器分析与设计

# 5.1 引言

这一章主要来介绍频率综合器中的另外一个重要模块"分频器",它是除压控振荡器之外工作频率最高的的模块。为了使压控振荡器的高频输出信号 fow与晶振的低频参考信号 free 比较,需要用到分频器对高频信号进行降频;为了得到正交的本振输出信号 I/Q,也需要用到分频器对输出信号进行正交处理。本章主要从这两个应用来介绍分频器的设计。

在分频器的设计时需要考虑很多问题:由于应用在宽带分数分频频率综合器中,所以要求分频器有较宽的工作频率范围;由于分频器各模块间延时的存在,所以电路之间的时序配合要求比较精确;因为分频器工作在最高频率,所以它的功耗是个不可避免的问题。此外,还需要确保分频器在各个工艺角以及温度变化下都能正常工作。

# 5.2 分频器设计

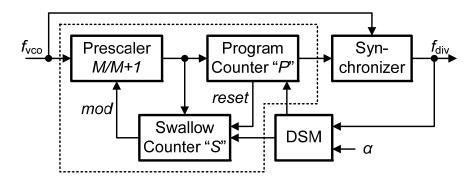

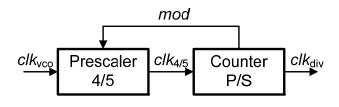

分频器的结构有很多种[27]。本设计采用双模可编程分频器结构,它由一个双模预分频器 M/M+1,一个可编程计数器 P 以及一个脉冲吞吐计数器 S 构成,如图 5-1 虚线框内所示。

图 5-1 ΔΣ 调制器控制的分数分频器

它的工作原理是:在电路重置后,双模预分频器工作在 M+1 模式。可编程计数器和脉冲吞咽计数器同时对预分频器的输出开始计数。当脉冲吞咽计数器计数到 S 个数以后,便通过控制信号 mod 使得双模预分频器工作在 M 模式。此时程序计数器与预分频器仍继续计数( $P \ge S$ ),直到程序计数器计满 P 个数。然后发出重置信号,完成一个周期的计数,电路重新开始计数[7]。基于双模预分频器的可编程分频器结构的分频比为

$$N = (M+1) \cdot S + M \cdot (P-S) = M \cdot P + S \tag{5.1}$$

为了能够实现分数分频,在多模可编程分频器的结构上,又引入了  $\Delta\Sigma$  调制器,如图 5-1 所示。它的工作原理是:在基于双模预分频器的可编程分频器的基础上,通过  $\Delta\Sigma$  调制器控制程序计数器和脉冲吞咽计数器。譬如先对输入的 A 个脉冲进行 N 分频,然后再对输入的 B 个脉冲进行 N+1 分频,那么等效的分频比为

$$N.\alpha = \frac{A+B}{A/N+B/(N+1)}$$

(5.2)

通过选择合适的 A 和 B,我们可以得到分频比在 N 和 N+1 之间的分数分频  $N.\alpha$ 。其中 N 表示整数部分, $\alpha$  表示分数部分。当然, $\Delta\Sigma$  调制器也会引入些其它问题,譬如产生高通量化噪声,以及容易受到程序计数器和脉冲吞咽计数器的编码方式的影响[28]。本论文对这些问题不做过多介绍。

在分频器的输出端引入了一个同步电路(Synchronizer),它可以减小由于信号抖动逐级叠加的影响[29]。一般采用同步触发器结构,由压控振荡器的输出信号同步。因此在输出端的信号抖动主要受到该同步电路的影响,从而减小了输出噪声。

### 5.2.1 4/5 预分频器

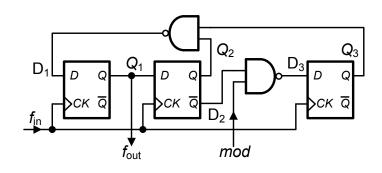

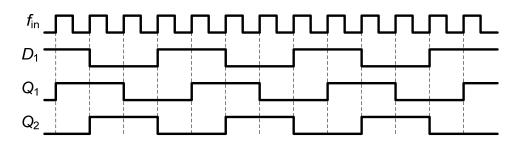

预分频器按结构可分为传统的同步计数器型,相位开关型[30]和注入锁定型[31]。传统的同步计数器型预分频器基于触发器结构,电路相对简单,但是随着频率的增加功耗也随之增大。相位开关型预分频器的工作频率较高,并且功耗相对较小,但是它会产生杂散,导致工作失常。注入锁定型预分频器的工作方式类似于注入锁定振荡器,功耗低,但是它的频率范围小,对工艺的变化敏感。由于本设计中压控振荡器的最大输出频率为 1.8GHz,频率并不是很高。所以采用结构相对简单的同步 4/5 预分频器,它由三个 D 触发器和两个与非门构成,其结构如图 5-2 所示。

图 5-2 同步 4/5 预分频器

当控制信号 mod 为 0 时,预分频器工作在 4 分频模式,此时第三个 D 触发

器被屏蔽。假设  $Q_1$  和  $Q_2$  的初始状态均为  $Q_3$  的初始状态均  $Q_4$  的初始状态为  $Q_4$  的初始状态为  $Q_5$  如图  $Q_5$  所示。

图 5-3 4/5 预分频工作在 4 分频模式

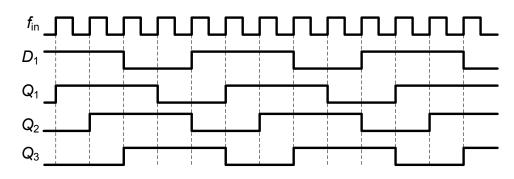

当控制信号 mod 为 1 时,预分频器工作在 5 分频模式,此时三个触发器都工作在最高频率,其时序如图 5-4 所示。

图 5-4 4/5 预分频工作在 5 分频模式

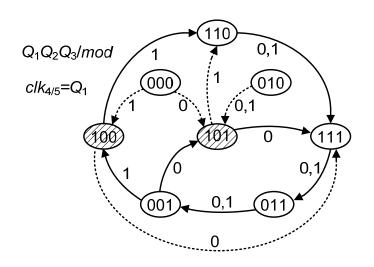

为了更好地理解 4/5 预分频器的工作过程,我们可以通过分析它的状态图,如图 5-5 所示。

图 5-5 4/5 预分频的状态图

输出信号  $Q_1$ , $Q_2$ 和  $Q_3$ 组合共有八个状态,当控制信号 mod 为 1 时,系统总能进入最外面的五个状态的循环,即 5 分频模式。同理,当控制信号 mod 为

0 时,系统可以立刻切换到四个状态的循环,即 4 分频模式。此外还可以看出系统不存在独立的死循环,尽管当  $Q_1Q_2Q_3$  为 000 或 010 时,状态不在上述循环内,但进过一个周期总能切换到正常的工作模式。

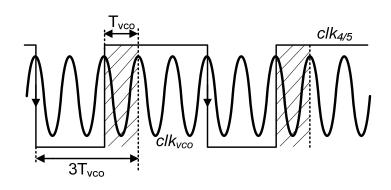

# 5.2.2 时序问题

在同步 4/5 预分频器的设计中,如图 5-6 所示, $clk_{vco}$  触发  $clk_{4/5}$ , $clk_{4/5}$  触发 mode,然后由 mod 反过来控制  $clk_{4/5}$ 。由于从  $clk_{vco}$  到  $clk_{4/5}$  再到 mode 存在延时  $t_d$ ,所以这种工作过程存在一个时序的问题。假设它们都是上升沿工作,如果  $t_d$ 大于一个  $clk_{vco}$  时钟周期,那么电路就可能会发生功能错误。

图 5-6 4/5 预分频中的延时问题

为了分析 4/5 预分频器的时序如何导致功能错误,我们来观察上一小节中的 状态图 5-5。 $clk_{4/5}$ 时钟信号也就是第一个触发器输出端  $Q_1$  的状态。从状态图的 两个循环中(图中以实线表示),我们发现,分频比为"4"和分频为"5"的关键 区别在于状态  $Q_1Q_2Q_3$  为 100 或 101 时。也就是在  $clk_{4/5}$  时钟信号跳变成高电平的第一个周期,如果此时 mod 信号为 1,则它的输出表现为 5 分频;如果此时 mode 信号为 0,则表现为 4 分频。也就是说,如果想让 4/5 预分频器按要求工作,那么 mod 信号必须在  $clk_4/5$  时钟信号变为高电平的第一个时钟周期结束前,给出一个确切的值。

假设图 5-6 中的计数器 P/S 是上升沿触发,那么  $clk_{vco}$ 到 mod 的延时  $t_d$  必 须控制在一个时钟周期  $T_{vco}$  以内,才能正常工作,如图 5-7 所示。为了扩大延时的裕度,降低数字布局布线以及综合的难度,我们采用的解决办法是,把计数器设置为下降沿触发。那么留给 mod 信号的延时  $t_d$  就变成了三个时钟周期  $T_{vco}$ 。

图 5-7 4/5 预分频对 mod 信号的延时要求

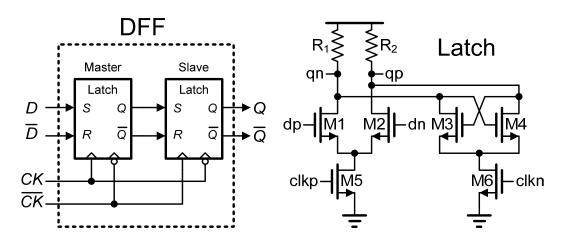

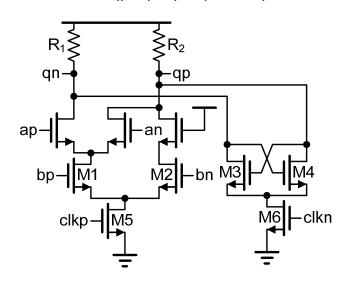

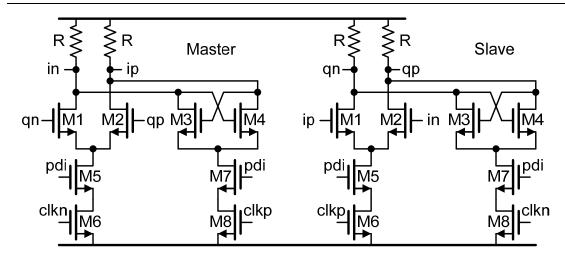

### 5.2.3 4/5 预分频器电路设计

常用的高速 D 触发器一般采用 CML 结构的锁存器,如图 5-8 所示。本设计采用电阻负载的 CML 结构,它的输出动态范围大,可以减缓后级输入信号对幅度的要求。并且去掉了尾电流源,提高了锁存器的速度。但是有一点需要注意,该结构的输出信号对温度和工艺的变化比较敏感。其工作过程为:在时钟的正半周,晶体管 M5 导通,M1 和 M2 对输入信号采样;在时钟的负半周,M6 导通,M3 和 M4 交叉耦合管通过正反馈的作用对采样信号进行锁存。从图中还可以看出,它采用主从结构。主级采用负锁存器,从级采用正锁存器。所以是一个正边沿触发的 D 触发器。

图 5-8 CML 结构的 D 触发器

为了减少 MOS 管的数目并提高速度,我们把图 5-2 中单独的与非门嵌入到 D 触发器中[27]。这里只需把 D 触发器主级锁存器换成图 5-9 结构的 CML 锁存器即可,其逻辑关系可表示为 qp=ap×bp, qn=an+bp。

图 5-9 集成与非门的 CML 锁存器结构

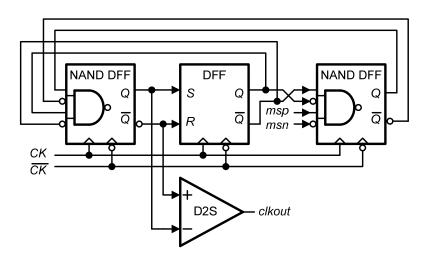

图 5-10 是同步 4/5 预分频的完整电路图, 其结构类似于图 5-2。所不同的是它把两个与非门嵌入到 D 触发器中, msp 与 msn 是差分输入的模式控制信号。

图 5-10 4/5 预分频器的实际电路

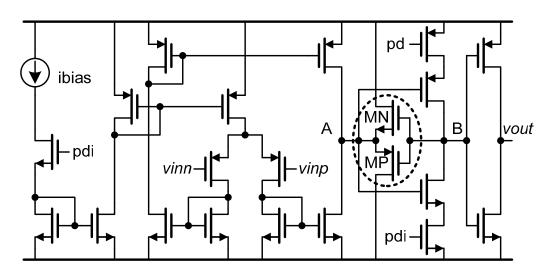

另外电路还引入了一个差分转单端模块 D2S,如图 5-11 所示。它主要是实现差分信号到单端信号之间的转换。然后驱动后级程序控制器和脉冲吞咽计数器。差分转单端电路其实就是一个简单的跨导放大器。这里只对虚线圈内的两个晶体管的作用做如下说明:由于 OTA 有较大的增益,即便很小的直流失配也会使得 A 点的直流电压过高或者过低。偏理反相器的阈值,导致后面的反相器不正常翻转。为了解决这个问题,于是引入这两个晶体管。当 A 点的直流工作点低于阈值时,MN 导通,MP 截止。电流从 MP 流入 A 点,使得 A 点电为升高。同理,如果 A 点直流工作点高于阈值电压,MP 导通,MN 截止。电流从 MN 管流出,使得 A 点电位被拉低。

图 5-11 差分转单端电路

# 5.2.4 4/5 预分频器版图

在 4/5 预分频器的版图设计中,考虑到电路的时序问题,尽量选择短的连线,以减小连线间的延时,如图 5-12 所示。

图 5-12 4/5 预分频器版图

### 5.2.5 仿真结果

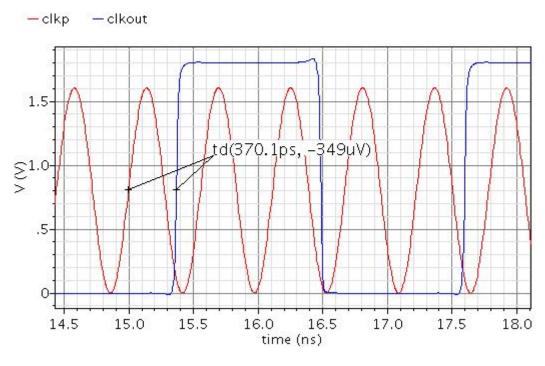

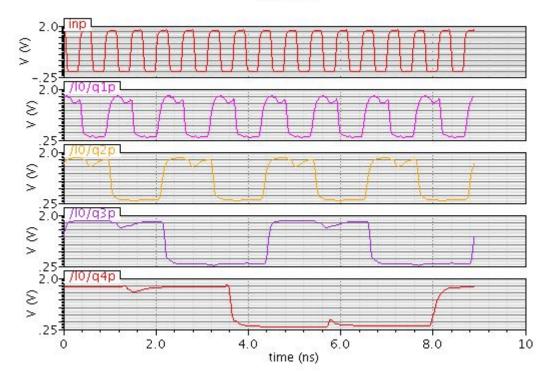

图 5-13 是在输入频率为 1.8G 的情况下, 电路工作在 5 分频模式的仿真图。

图 5-13 5分频仿真结果

图 5-16 是在输入频率为 1.8G 的情况下, 电路工作在 4 分频模式的仿真图。

#### division 4

图 5-14 4 分频仿真结果

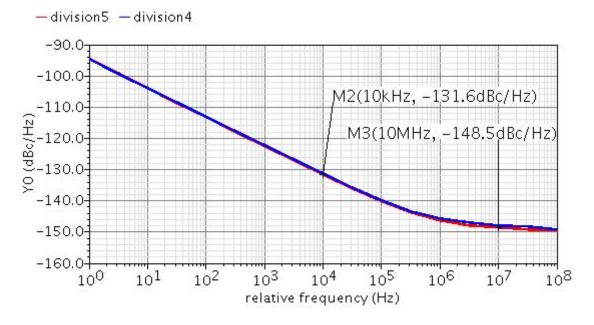

图 5-16 的相位噪声仿真结果表明,电路工作在 4 分频或者 5 分频的噪声差异不是很明显。

#### phase noise

图 5-15 4/5 预分频器的相位噪声

# 5.3 正交分频器设计

本项目设计的数字电视调谐器 DTV-Tuner 采用零中频结构,需要接受来自 UHF/VHF 频段中的数字电视信号。它的频率范围为 48M~869MHz。这给频率综合器的设计带来了很多挑战:首先,它需要达到很高的频率范围。本论文设计的压控振荡器 VCO 本身不可能完成这个任务。并且还需要满足一定相位噪声和积分相位误差的要求。然后,对于频率调制或者相位调制信号,下变频必须提供正交输出 I/Q,并且确保 I/Q 两路的正交匹配特性。这也是本设计中最为关键的部分。针对上面的问题,我们考虑使用二分频器电路。因为,一方面它可以扩展频率范围,另一方面,也可以提供我们需要的正交 I/Q 信号。

本小节主要就正交分频器的设计展开讨论。首先介绍I/Q 失配对系统的影响,然后分析其具体电路结构,并指出设计中的注意点。

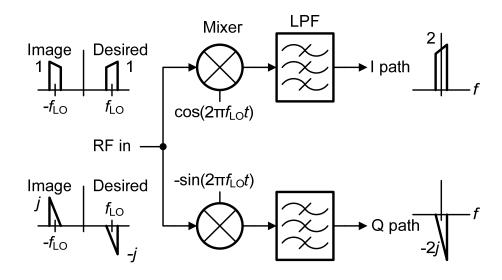

#### 5.3.1 I/Q 失配的影响

零差结构的接收机的结构相对简单,如图 5-16 所示。射频输入信号通过与正交的本振信号混频,同时产生同相的 I 信号和正交 Q 信号分量。然后经过滤波器滤除带外信号,变换成数字形式进行后续处理。它不像外差结构中存在的镜像问题以及需要用到难以集成的 SAW 滤波器。但是直接变换频谱到零中频会遇到很多问题,包括自混频对本振的影响,直流失调严重,I/Q 失配,偶数阶失真等。

图 5-16 正交零中频混频

为了具体了解 I/Q 不匹配产生的效应,我们假设射频输入信号  $x_{in}(t)=A\cos\omega_c t+A\sin\omega_c t$ ,得到 I/Q 两路的本振信号

$$X_{\text{LO,I}}(t) = (1+\varepsilon)\cos(\omega_c t + \theta) \tag{5.3}$$

$$X_{\text{LO,Q}}(t) = (1 - \varepsilon)\sin(\omega_c t - \theta)$$

(5.4)

其中  $\varepsilon$  和  $\theta$  分别表示幅度和相位的误差,如图 5-17 所示。经过混频器混频,然后滤波得到 I/Q 两路基带信号为

$$x_{i}(t) = a(2+\varepsilon)\cos\theta - b(2+\varepsilon)\sin\theta$$

(5.5)

$$x_{Q}(t) = -a(2-\varepsilon)\cos\theta + b(2-\varepsilon)\sin\theta$$

(5.6)

图 5-17 I/Q 失配对解调后的数字信号的影响

从图 5-17 可以看出,增益误差只是改变了调制后数字信号的幅度。并不影响调制的结果。但是相位误差的不平衡则会受到其他信道的叠加,使得数字信号

包含的信息被破坏。如果 I/Q 两路信号是不相关的,则会从本质上降低信噪比。为了衡量 I/Q 不匹配效应的影响,我们引入镜像抑制比(Image Reject Ratio, IRR) 这个概念[7]。它定义为输出端  $P_{\text{im}}/P_{\text{sig}}$  与输入端  $P_{\text{im}}/P_{\text{sig}}$  的比值,其中  $P_{\text{im}}$  表示镜像信号的平均功率,  $P_{\text{sig}}$  表示信号的平均功率。如果  $\varepsilon$ «A 和  $\theta$ «1rad,则可以化简为

$$IRR = \frac{\left(\varepsilon/A\right)^2 + \theta^2}{4} \tag{5.7}$$

上述这个表达式,不仅可以包含来自本振信号的不匹配,而且包含 I/Q 两路在经过低通滤波器等其他模块作用后的不匹配。本设计中,我们要求镜像抑制比在-40dB 以下,这要求本振信号提供的相位误差至少要在 1°以内。

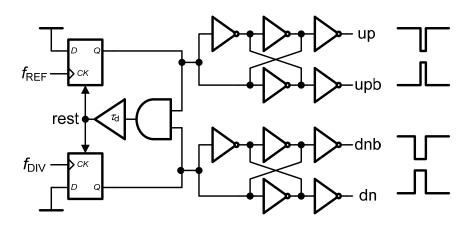

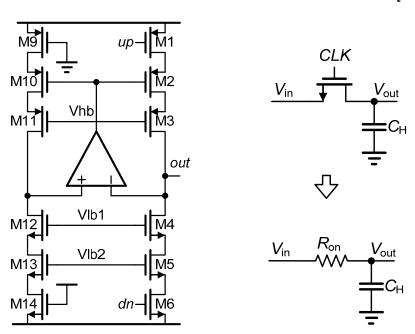

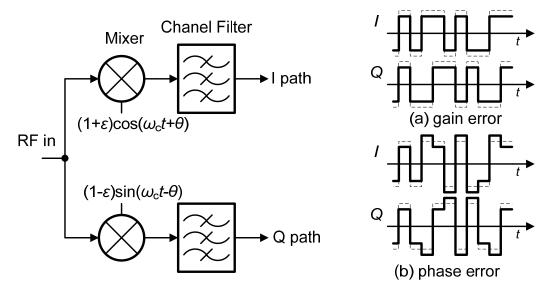

### 5.3.2 I/Q 分频器结构

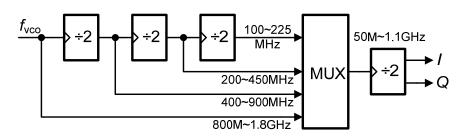

在文献[32]中,作者采用了如图 5-18 所示的 I/Q 分频器结构。前三个二分频电路级联,每个二分频电路都输出正交信号,然后通过一个多路选择电路 MUX来控制实现 2、4、8 和 16 分频。从而实现 50~480MHz 的信号正交信号。

图 5-18 I/Q 分频器基本框架图

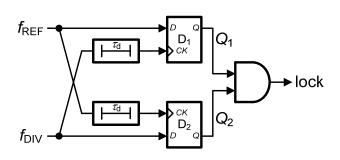

上述设计中的多路选择器采用 CML 类型的反相器。一方面,功耗较大;另一方面,需要根据分频比切换不同的上拉电阻。而电阻的阻值变化很大,这会引入较大误差。在该结构中,二分频器的灵敏度问题比较严重。随着压控振荡器频率的升高,其幅值相应减小。但是,二分频器随着频率升高对输入信号的幅度要求变高,所以需要特别注意二分频器在率范围内能否正常工作。

图 5-19 改进的 I/Q 分频器框架图

针对上述问题,本论文设计的 I/Q 分频器从两个方面对电路进行了改进,其框架如图 5-19 所示。

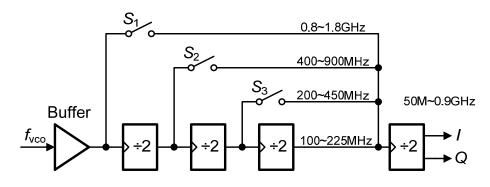

首先,在电路的输入端口添加了一个缓冲器。一方面,它对输入信号进行放大整形处理,得到比较理想的方波,从而减轻了电路受二分频器灵敏度特性的约束。另一方面,它减轻了压控振荡器的输出直接耦合的影响。另外,压控振荡器的输出直接对除二分频器的直流偏置比较困难,这也是引入缓冲器的另一个好处。需要注意的是,增加负载对压控振荡器工作频率的影响,索性仿真表明其影响可以忽略。

其次,用开关电路  $S_1 \sim S_3$  代替多路选择器,具体电路如图 5-20 所示。它同样对各级的输出信号进行放大整形,从而减小对下一级二分频器的性能的要求。采用 RC 耦合电路解决开关的自身偏置问题。其中虚线框内 M2 和 M3 是为了防止第二级输入耦合到输出。因为开关电路  $S_1 \sim S_3$  共用一个输出,即便开关关断的时候,由于耦合作用也会影响 I/Q 的匹配性能。如果没有这两个管子的隔离作用,在前仿中,我们发现 I/Q 的相位不匹配就已经超过了  $2^\circ$  。 当然,这两个管子也会对开关速度产生一定的影响。由于缓冲器的设计不同于开关电路需要考虑其他开关耦合的影响。所以我们在缓冲器的设计中去掉了这两个管子,以此来提高速度。

图 5-20 缓冲器电路/开关电路

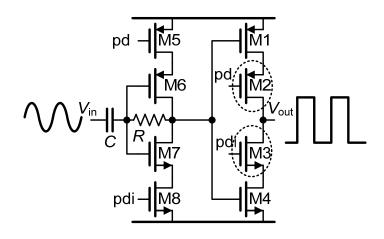

#### 5.3.3 二分频器电路

图 5-21 是 I/Q 分频器的核心电路,有两个 CML 锁存器构成。主级采用负锁存器,从级采用正锁存器。所以是一个正边沿触发的二分频电路。它的每一级都使用差分时钟工作,在时钟的正半周,晶体管 M6 导通,M1 和 M2 对输入信号采样。在时钟的负半周,M8 导通,M3 和 M4 交叉耦合管通过正反馈的作用对采样信号进行锁存。

图 5-21 CML 结构的二分频电路

在设计 I/Q 分频器时,需要特别关注两个问题: 灵敏度和正交匹配。接下来 我们分别来加以分析。

# 1) 灵敏度特性

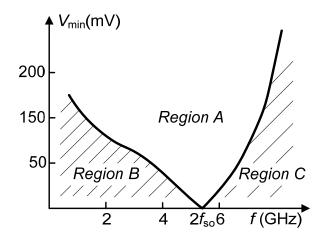

灵敏度是指,在输入不同频率的正弦信号时,如果希望分频器能够正常工作,那么对输入信号的幅度有一定的要求。如果将输入信号的频率与其最小的幅度关系描成曲线[33],就如图 5-22 所示。其中横坐标表示输入信号的频率,纵坐标表示能使分频器工作的最小幅度。CML 结构的分频器具有自激振荡特性。在输入时钟信号幅度为零,且只提供直流电平的情况下,分频器会在  $f_{so}$  频率处产生自激振荡。

图 5-22 分频器的灵敏度曲线

分频器的正常工作有一个频率范围,也就是上图的 A 区域。如果输入信号落在 B 区域,一方面由于信号幅度不够大,使得分频器没法正常采样。另一方面,如果信号的斜率太小,就无法实现电流的快速切换。在输入信号过零点,采样管和锁存管同时导通,就会被自激振荡所破坏。如果输入信号落在 C 区域,

分频器电路节点上的充放电时间常数超过输入信号的时钟周期,也会导致电路无法正常工作。于是,在设计时一般把分频器的工作频率设定在  $2f_{so}$  附近,最好不要超过  $2f_{so}$  太多。否则,分频器对输入信号幅度的要求会骤然增加。

分频器的自激振荡频率  $f_{so}$  越高,工作频率也就越高,对于输入信号的幅度要求也就相对较小。在 CML 分频器中,交叉耦合管 M1~M4 的尺寸选择决定了分频器是否自激振荡[34]。随着交叉耦合管尺寸的减小,电路的极点从右半区域逐渐向虚轴靠近。如果尺寸小到一定程度,极点移动到左平面,自激振荡也就停止了。

分频器的工作频率和功耗,主要由晶体管的尺寸和电阻 R 的大小决定。 首先,我们来考察影响工作频率的几个参数间的关系

$$\tau \propto R \cdot C_{total} \propto \left(\frac{\Delta V}{I_{CML}}\right) \cdot W_{M1\sim M4} \propto \Delta V$$

(5.8)

其中  $\Delta V$  为差分对管的输出摆幅;  $I_{CML}$  为 CML 锁存器的源电流,它与晶体管 M6、M8 的大小相关;  $W_{M1\sim M4}$  是差分管 M1、M2 和交叉耦合管 M3、M4 的尺寸大小。输出节点的总电容  $C_{total}$  主要由差分对管的栅源电容  $C_{gs,d}$ 、栅漏电容  $C_{gd,d}$ 、漏到 衬底电容  $C_{db,d}$ ,交叉耦合管的栅源电容  $C_{gs,c}$ ,栅漏电容  $C_{gd,c}$ ,栅到衬底电容  $C_{db,c}$ ,后一级锁存器的负载电容  $C_{load}$ ,以及输出点的寄生电容  $C_p$  组成

$$C_{total} \approx 2C_{ad,d} + C_{as,d} + C_{db,d} + 4C_{ad,c} + C_{as,c} + C_{db,c} + C_{load} + C_{p}$$

(5.9)

所以总电容  $C_{total}$  与  $W_{M1\sim M4}$  的大小也有正相关的关系。从上式还可以看到,交叉耦合管贡献的栅漏电容为  $4C_{gd,c}$ 。因此为了提高工作频率,往往减小作为锁存功能的交叉耦合管的尺寸。仿真表明,差分对管 M1、M2 和交叉耦合管 M3、M4 的最佳尺寸比例大概为 6:5[35]。

从公式(5.8)还可以看到,分频器的工作频率也取决与电阻 R 的大小。实际上,改变 M1~M4 管的尺寸到一定程度后对工作频率的贡献已经很小。因为寄生等电容占据主导地位,它不随着尺寸的减小而减小。此时,我们主要通过改变电阻 R 的大小来优化分频器的工作频率。

需要说明的是,本设计直接通过优化输入信号,使得第一级二分频电路和最后一级二分频电路对输入信号的要求大大降低。

然后,我们来考察影响分频器功耗的因素。显然,我们可以通过减小差分输出信号的幅度来减小功耗。一方面我们可以减小电阻来实现;另一方面,我们也可以减小 CML 锁存器的源电流,通过减小 M6、M8 管的尺寸来实现。但是它也会影响分频器的工作频率。

在提高分频器的工作频率和减小功耗的过程中,我们需要关注二分频器间的级联问题。如果分频器的输出摆幅不够,很可能导致后级分频器没法正常工作,甚至会影响后级分频器输入管的直流偏置问题。所以,分频器的优化需要通过仿

真来协调各种性能之间的关系。

### div sensitivity 16

— sensitivity<0> — sensitivity<1>

图 5-23 灵敏度仿真曲线

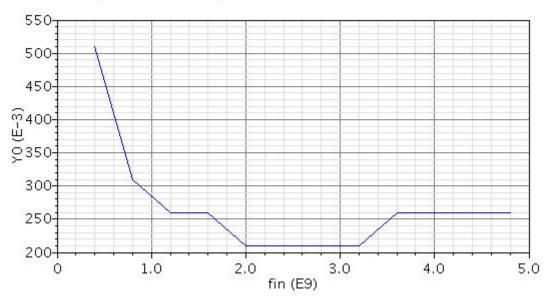

图 5-23 是本文仿真的灵敏度曲线。输入频率为 1.8G,工艺角为 tt, 室温为 25°C, I/Q 分频器工作在 16 分频模式。其中纵坐标是输入信号的电压幅度,横坐标是输入信号的频率。

#### 2) 匹配特性

I/Q 分频器的正交匹配特性在小结 5.3.1 已经讨论了很多,这里主要就电路如何优化设计展开。

首先,从电路设计本身出发,来尽量减小引起正交不匹配的因素。

考虑到开关  $S_1 \sim S_3$  共用一个输出节点,不同分频器间的信号会耦合到输出节点。所以在本电路设计中,尤其是开关电路的最后一级,在输出端的两侧分别串入一个晶体管,起隔离作用。这个技术在上文中已经介绍过。

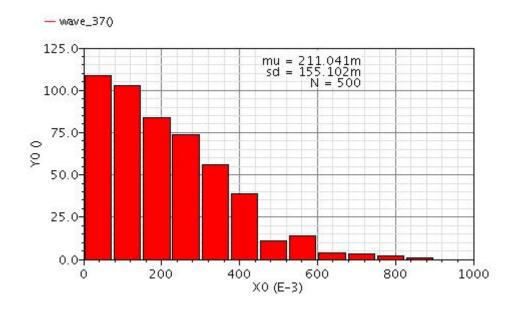

本文设计的I/Q分频器实际上在最后一级二分频电路中才产生我们需要的正交信号。而前面三个分频器,主要是为后一级二分频器提供差分输入信号。所以,我们把设计的重心放在了最后一个二分频电路上。正如第四章中讨论的,我们最为关心的是管子间的匹配问题。而我们唯一采取的办法就是通过增大晶体管的尺寸以及电阻的尺寸,来减小器件间的不匹配程度。如图 5-24 所示,通过 Monto Carlo 仿真得到分频器的正交输出相位差的统计分布。对相位差进行绝对值处理,所以统计分布表现为高斯分布的正半轴部分。可以看到,在相位差的 3σ 处,I/Q 分频器的正交相位差控制在 0.5°以内。

图 5-24 I/Q 分频器正交匹配特性 Monto Carlo 仿真结果

然后,我们通过版图设计来减小引起正交不匹配的因素。实际上,版图的对称,以及走线的规划,是影响正交的匹配特性的最大因素。因此,在设计版图时需要确保晶体管和信号线的对称性。特别是交叉耦合管之间的连线,我们采用如图 5-25 中间部分所示的桥路结构;对于差分管 M1、M2 和交叉耦合管 M3、M4,我们采用了四象限交叉共质心画法;而对输入时钟管 M6、M8 采用叉指结构;为了确保晶体管周围的环境类似,同时也使用了一些 dummy 管。

图 5-25 二分频器版图

#### 5.3.4 I/Q 分频器版图

前面已经介绍过,I/Q 分频器的正交相位误差对电路的对称性要求比较高,尤其是在版图的设计过程中。上一小节,我们对单个二分频器电路的版图有过简要说明。但是对于整个 I/Q 分频器的整体布局,它的对称性也是至关重要的。在图 5-26 中,我们把分频器每级的开关对称地安置在二分频器的两侧,这样可以确保每级输出线路的匹配。

最后一级二分频器电路的尺寸是前面几级二分频器电路的两倍。而且最后一级二分频器的正交输出信号的连线需要仔细规划。在与混频器连接的路径中,要减小相互之间的耦合,以及外界对连线的干扰,同时确保它们的匹配。

图中下方是一个数字电路,用于选择导通开关。同样的,它被安置在深井中。为了减小对左右两路的影响差异,放置在版图的中间位置。

图 5-26 I/Q 分频器版图

#### 5.3.5 仿真结果

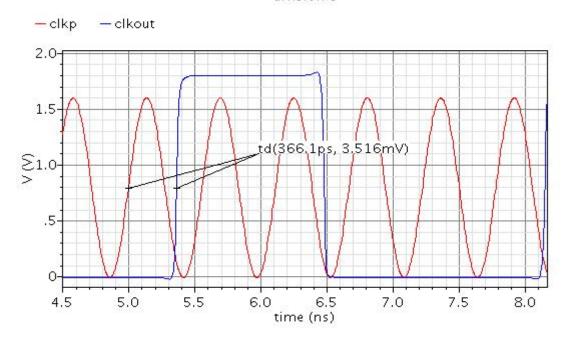

图 5-27 是 I/Q 分频器工作在 16 分频模式下的仿真图。

图 5-27 I/Q 分频器仿真波形

在工艺角为 tt, 室温为 25°C 的环境下, 输入频率为 1.8GHz, 我们得到 I/Q 分频器后仿结果。

|          |         | 2 分频   | 4 分频   | 8 分频   | 16 分频  |

|----------|---------|--------|--------|--------|--------|

| I/Q 正交l  | 匹配(max) | 0.2°   | 0.06°  | 0.03°  | 0.01°  |

| 相位噪声     | @10kHz  | -119.4 | -125.3 | -131.1 | -136.8 |

| (dBc/Hz) | @10MHz  | -155.6 | -158.1 | -160.5 | -162.7 |

| 功耗(mW)   |         | 9.09   | 8.79   | 9.23   | 10.20  |

表 5-1 I/Q 分频器后仿结果

### 5.4 本章小结

- 1) 详细介绍了一种同步 4/5 预分频器电路的设计,从状态图出发分析了电路的时序问题。并给出了相应的电路设计版图及仿真结果;

- 2) 详细介绍了 I/Q 分频器的设计。分析了电路的正交匹配特性以及灵敏度特性,并针对这两个方面对电路进行设计优化。最后给出了 I/Q 分频器的电路设计版图以及仿真结果;

# 第六章 总结与展望

### 6.1 工作总结

本论文围绕 ΔΣ 分数分频频率综合器展开,主要分析和设计了其中的鉴频鉴相器、电荷泵、分频器以及 I/Q 分频器等电路模块。该频率综合器应用于一款数字移动电视的接收机,为其提供正交的本振信号。本论文研究的主要内容为:

- 1) 对频率综合器做了简要的介绍,包括:指出了整数分频器和分数分频器各自存在的问题;介绍了频率综合器设计中的几个重要参数,并且对环路的相位噪声模型进行了详细的分析;总结了频率综合器的设计流程。

- 2) 总结了几种鉴频鉴相器的结构,重点介绍了基于电荷泵的鉴频鉴相器,包括:分析了鉴频鉴相器中遇到的非理想效应,并给出了相应的解决方案;分析了电荷泵型鉴频鉴相器的非线性特性,并提出了一种降低非线性的技术;讨论了电荷泵的导通时间对带内噪声的影响,在设计中加入了对导通时间选择的功能。

- 3) 通过设计源端开关电荷泵单元,简化了全差分电荷泵电路,并且分析了全差分电荷泵的环路特性;针对电路设计中遇到的非理想因素采取了相应的解决方案;详细分析了晶体管间的 mismatch 对电荷泵电路性能的影响,得出了晶体管间的 mismatch 在整个电荷泵上下电流匹配特性中占主要地位的结论;分析了电荷泵电流大小对整个环路性能的影响。

- 4) 分析了 4/5 预分频器的工作时序问题,指出上升沿触发的 P/S 计数器可以使 预分频器的延迟冗余增加到 3 个时钟周期;针对 I/Q 分频器对正交相位匹配 的严格要求,采用 CML 结构的除二分频器电路,并且设计了一种全新结构 的 I/Q 分频器电路,可以减小工艺波动对电路性能的影响;分析了基于 CML 结构的分频器的灵敏度特性,并且在 I/Q 分频器的输入端引入一个对输入信号的放大整形电路很好的解决了该灵敏度要求的限制。

- 5) 最后,给出了相应电路模块的版图以及仿真结果,验证了电路功能的正确性。本文参与设计的频率综合器在 TSMC 的 0.18μm 的工艺下成功流片,频率范围覆盖 0.8GHz~1.8GHz,总的芯片面积为 0.9mm×0.9mm。其中鉴频鉴相器和电荷泵的功耗为 1.4mA,4/5 预分频器的功耗为 1.2mA, I/Q 分频器的功耗为 4~6mA。环路滤波器的带宽为 75kHz。I/Q 分频器的正交相位误差小于 0.5°。带内相位噪声低于-100dBc/Hz。锁定时间小于 30μs。

### 6.2 未来展望

在以上工作的基础上,可以继续展开以下的研究工作:

- 1) 相对于单端结构的电荷泵电路,基于全差分结构的电荷泵虽然在性能上有其优势,但结构更为复杂。考虑到管子间的 mismatch 对电荷泵性能的关键影响,我们可以从减小管子间 mismatch 的方向设计单端结构的电荷泵电路,在达到同样性能的情况下,使得电路的设计变得更加简单。

- 2) 4/5 预分频器电路虽然能够满足应用的要求,但是它对带外量化噪声的抑制不是很好。可以考虑选择步长为 0.5 的 4/4.5 预分频器,甚至更小步长的预分频器,来降低 ΔΣ 调制器引起的量化噪声。

- 3) I/Q 分频器的工作电流在 5mA 左右,而且随着输入频率和分频比的增大而增大,这对于低功耗的接收机而言是相当大的。所以在电路的设计中,可以考虑采用功耗更小的除二分频器和开关电路;或者通过数字电路控制选择最小的输入电压和较小的分频比来得到所需的正交本征信号。

# 参考文献

- [1] Iason Vassiliou, Kosits Vavelidis, etc., "A 65 nm CMOS Multistandard, Multiband TV Tuner for Mobile and Multimedia Applications", *IEEE J. Solid-State Circuits*, vol.43, no.7, pp.1522-1533, Jul.2008.

- [2] F. M. Gardner, *Phaselock Techniques. Second Ed.*, New York: Wiley & Sons, 1979.

- [3] Venceslav F.Kroupa, *Frequency Synthesis: Theory, Design & Applications*, Griffin, 1973.

- [4] Dean Banerjee, *PLL Performance, Simulation and Design Handbook* (4th ed.), National Semiconductor, 2006.

- [5] Tsung-Hsien Lin, Ching-Lung, Yao-Hong Liu, "Dynamic Current-Matching Charge Pump and Gated-Offset Linearization Technique for Delta-Sigma Fractional-N PLLs", *IEEE. Trans. Circuits Syst. I*, Reg. Papers, vol.56, no.5, pp.877-885, May.2009.

- [6] 吕磊,"射频接收机中分数分频频率综合器的研究和设计", 复旦大学博士学位 论文, 2009.

- [7] B.Razavi, RF Miroelectronics, Upper Saddle River, NJ: Prentice Hall, 1998.

- [8] W.Khalil, H.Hedayati, B.Bakkaloglu, S.Kiaei, "(INVITED)Analysis and Medeling of Noise Folding and Spurious Emission in Wideband Fractional N Synthesizers", IEEE Radio Frequency Integrated Circuits Symposium, 2008.

- [9] Carlos Quemada, Guillermo Bistué, Iňigo Adin, *Design Methodology for RF CMOS Phase Locked Loops*, Artech House 2009.

- [10] H.Perrott, D.Trott, G.Sodini, "A Modeling Approach for Σ-Δ Fractional-N Frequency Synthesizers Allowing Straightforward Noise Analysis", *IEEE J. Solid-State Circuits*, vol.37, no.8, Aug.2004.

- [11] P.Hein, W.Scott, "z-Domain Model for Discrete-Time PLL's", *IEEE. Trans. Circuits Syst*, vol.35, no.11, Nov.1988.

- [12] F. M. Gardner, "Charge-Pump Phase-Locked Loop", *IEEE Trans. Comm.*, vol.COM-28, pp.1849-1858, Nov.1980.

- [13] 喻学艺,"相位及延时锁定环中的量化噪声抑制技术",清华大学博士学位论文, 2009.

- [14] B.Razavi, *Design of Analog CMOS Intergrated Circuits*, Xi'an Jiaotong University Press, 2003.

- [15] Craninckx,J., and M. Steyaert, Wireless CMOS Frequency Synthesizer Design, Norwell, MA: Kluwer Academic Publishers, 1998.

- [16] D.Banerjee, *PLL Performance, Simulation and Design, 2<sup>nd</sup> ed.*, National Semiconductor, 2001.

- [17] A.D.Riley, M.Filiol, Qinghong Du, Juha Kostamovaara, "Techniques for

- In-Band Phase Noise Reduction in  $\Delta\Sigma$  Synthesizers," *IEEE. Trans. Circuits Syst.II*, Reg. Papers, vol.50, no.11, pp.794-803, NOV.2003.

- [18] H.Hedayati, Bertan Bakkaloglu and W.Khalil, "Closed Loop Nonlinear Modeling of Wideband Fractional-N Frequency Synthesizers", *IEEE Trans. Microwave Theory and Techniques*, vol.54, no.10, Oct.2006.

- [19] E.Temporiti, G.Albasini, I.Bietti, R.Castello, and M.Colombo, "A 700-kHz bandwidth ΣΔ fractional synthesizer with spurs compensation and linearization techniques for WCDMA applications", *IEEE J. Solid-State Circuits*, vol.389, no.9, pp.1446-1454, Sep.2004.

- [20] H.Huh, Y.Koo, etc., "Comparison Frequecry Doubling and Charge Pump Matching Techniques for Dual-Band ΔΣ Fractional-N Frequency Synthesizer", IEEE J. Solid-State Circuits, vol.40, no.11, pp.2228-2236, Nov.2005.

- [21] B.Terlemez, C.Sandner, "The design of a differential CMOS charge pump for high performance phase-locked loops," in *Proc. Int. Symp. Circuits Syst.*, May 2004, vol.4, pp.IV-561-4.

- [22] W.Rhee, "Desigh of high-performance CMOS charge pumps in phase locked loops", *Proceedings of the 1999 IEEE International Symposium on Circuits and Systems*, vol.2, pp.545-548,1999.

- [23] 孟令部,"2~2.4 GHz 分数分频频率综合器设计",复旦大学硕士学位论文,2011.

- [24] Pavan Kumar Hanumolu, Merrick Brownlee, Kartikeya Mayaram, Un-Ku Moon, "Analysis of Charge-Pump Phase-Locked Loops", *IEEE. Trans. Circuits Syst-I*, vol.51, no.9, Sep.2004.

- [25] A.K.Ong, V.T.Prodanov, M.Tarsia, "A Method for Reducing the Variation in "On" Resistance of a MOS Sampling Switch", *IEEE International Symposium on Circuits and Systems*, vol.5, p.437-440, May.2000.

- [26] W.Sansen, Analog Design Essentials, Springer 2006.

- [27] Cicero S.Vaucher, Igor Ferencic, Matthias Locher, Sebastian Sedvallson, Urs Voegeli, Zhenhua Wang, "A Family of Low-Power Truly Modular Programmable Dividers in Standard 0.35-µm CMOS Technology", *IEEE J. Solid-State Circuits*, vol.35, no.7, pp.1039-1045, Jul.2000.

- [28] 吕磊, 闵昊, 唐长文, "一种应用于分数分频频率合成器的脉冲吞计数器", 发明 专利, 申请号: 200910050627.7

- [29] S.Levantino, L.Romanó, S.Pellerano, C.Samori, and A.L.Lacaita, "Phase noise in digital frequency dividers", *IEEE J. Solid-State Circuits*, vol.31, no.5, pp.749-784, May.1996.

- [30] J.Cranincks, M.Steyaert, "A 1.75GHz/3V Dual-Modulus Divide-by-128-129 Prescaler in 0.7-μm CMOS," *IEEE J. Solid-State Circuits*, vol.31, pp. 890-897, July.1996.

- [31] H. Rategh, H. Samavati, and T. Lee, "A CMOS frequency synthesizer with an injection-locked frequency divider for a 5-GHz wireless LAN receiver," IEEE

- J. Solid-State Circuits, vol.35, pp.780-787, May.2000.

- [32] 黄兆磊,"频率综合器中分频器的研究与设计",复旦大学硕士论文,2011.

- [33] Ullas Sigh, M.Green, "Dynamic of high-frequency CMOS dividers", *IEEE Internatinal Symposium on Circuits and Systems*, vol.5, pp.421-424, May.2002.

- [34] W.Fang, et al., "An analytical maximum toggle frequency expression and its application to optimizing high speed ECL frequency dividers", *IEEE J. Solid-State Circuits*, vol.25, pp.920-931, Aug.1990.

- [35] Yanping Ding, Keneth K.O, "A 21-GHz 8-Modulus Prescaler and a 20-GHz Phase-Locked Loop Fabricated in 130-nm CMOS", *IEEE J. Solid-State Circuits*, vol.42, no.6, pp.1240-1249, Jun.2007.

## 致谢

十几年的学习生涯转瞬即逝,仿佛昨日。在复旦求学的最后阶段由衷地感谢曾经相处过的老师和同学们。

首先,感谢我的导师唐长文副教授对我的悉心指导,他严谨的治学态度、专 注的技术热情以及坚忍不拔的毅力将鞭策着我不断学习。

其次,感谢杨涛和卓晨飞同学在本论文写作中提供的热情帮助;感谢王明贵和孙玉香同学,与你们的讨论使我对电路有了更进一步的理解;感谢唐聪、张伟、黄实、董叶以及张唯一同学,与你们的交流让实验室变得不再枯燥;感谢黄兆磊和饶敏师兄以及吴琦师姐在电路上提供的指点;另外还要感谢廖泽鑫和黄现等同学,从你们身上看到了作为朋友的可贵。

最后,感谢我的父母,无须多言,由于你们给予的关爱,才使得我不断前进。

## 论文独创性声明

| 本论文是我个人在导师指导下进行的研究工作及取得的研究成果。论文中除   |

|-------------------------------------|

| 了特别加以标注和致谢的地方外,不包含其他人或其它机构已经发表或撰写过的 |

| 研究成果。其他同志对本研究的启发和所做的贡献均已在论文中作了明确的声明 |

| 并表示了谢意。                             |

| 作者签名:    | 日期:    |  |

|----------|--------|--|

| 11 H H • | H /93• |  |

## 论文使用授权声明

本人完全了解复旦大学有关保留、使用学位论文的规定,即:学校有权保留 送交论文的复印件,允许论文被查阅和借阅;学校可以公布论文的全部或部分内 容,可以采用影印、缩印或其它复制手段保存论文。保密的论文在解密后遵守此 规定。

| 作者签名: 导 | 师签名: | 日期: |

|---------|------|-----|

|---------|------|-----|