# 模拟集成电路设计原理

# (Principle of Analog Integrated Circuit Design, INF0130025.02)

2014年11月13日

唐长文 教授

zwtang@fudan.edu.cn

http://rfic.fudan.edu.cn/Courses.htm

复旦大学/微电子学院/射频集成电路设计研究小组

版权©2014, 版权保留, 侵犯必究

# 运算放大器的系统设计

#### 目录

- 单级OTA的设计

- CMOS密勒OTA的设计

- GBW和相位裕度的设计

- 其他指标:输入范围、输出范围、SR...

Ref.: W. Sansen: Analog Design Essentials, Springer 2006

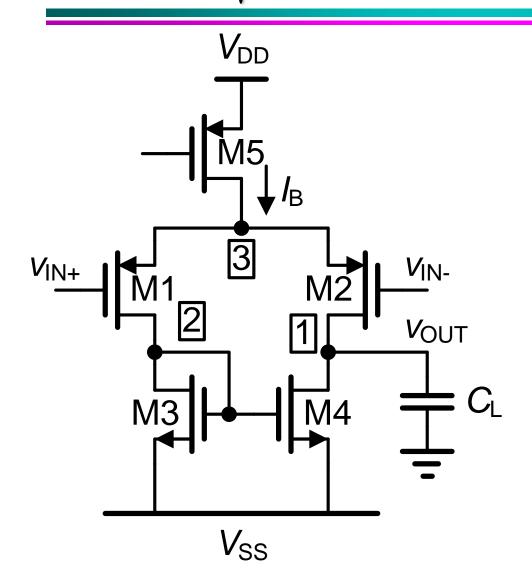

### CMOS单级OTA: GBW

$$A_{\rm V}=g_{\rm m1}\frac{r_{\rm DS}}{2}$$

如果:  $r_{DS2} = r_{DS4} = r_{DS}$

$$BW = \frac{1}{2\pi \frac{r_{DS}}{2}(C_L + C_{n1})}$$

$$GBW = \frac{g_{m1}}{2\pi(C_L + C_{n1})}$$

### CMOS OTA: 最大GBW

$$GBW = \frac{g_{m1}}{2\pi C_L} \qquad g_{m1} = \frac{I_B}{V_{GS1} - V_T}$$

$$GBW_{\text{max}} = \frac{I_{\text{B}}}{V_{\text{GS1}} - V_{\text{T}}} \frac{1}{2\pi C_{\text{L}}}$$

$$C_L = 1 \text{ pF}$$

$V_{OUT}$

$I_B = 10 \text{ } \mu\text{A}$

$\Rightarrow GBW_{\text{max}} \approx 10 \text{ MHz}$

[8]

$$FOM = \frac{GBW \cdot C_{L}}{I_{B}}$$

$$= 1000 \text{ MHzpF/mA}$$

[800]

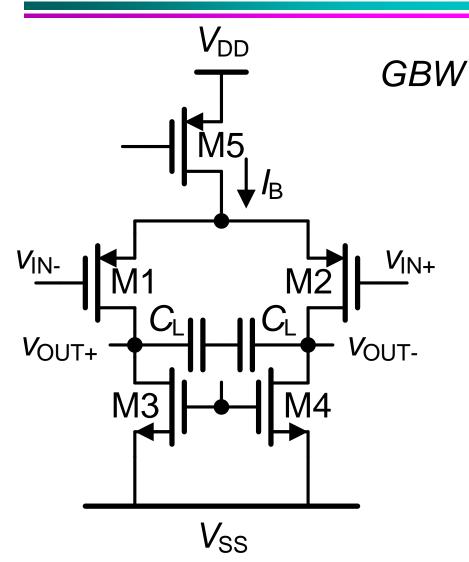

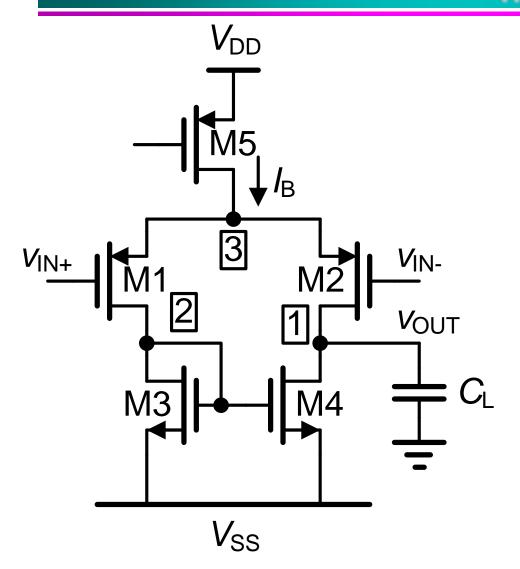

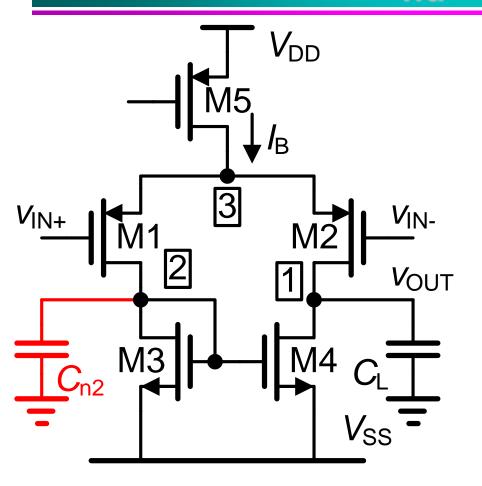

# CMOS单级OTA: f<sub>nd</sub>

$$GBW = \frac{g_{\text{m1}}}{2\pi(C_{\text{L}} + C_{\text{n1}})}$$

$$f_{\rm nd} = \frac{g_{\rm m3}}{2\pi C_{\rm n2}}$$

$$C_{\text{n2}} \approx 2C_{\text{GS3}} + C_{\text{DB3}} + C_{\text{DB1}}$$

$\approx 4C_{\text{GS3}}$

$$f_{\rm nd} \approx \frac{f_{\rm T3}}{4}$$

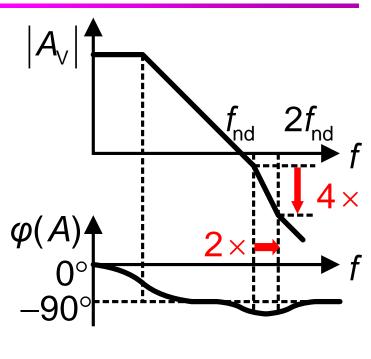

# CMOS OTA: $f_{nd}$

$$f_{\rm nd} = \frac{g_{\rm m3}}{2\pi C_{\rm n2}}$$

$$PM = 90^{\circ} - \arctan(\frac{GBW}{f_{\text{nd}}}) + \arctan(\frac{GBW}{2f_{\text{nd}}}) \approx 85^{\circ}$$

### CMOS单级OTA: 设计 1

已知: GBW = 100 MHz 和 C = 2 pF

工艺:  $L_{min} = 0.35 \ \mu m \cdot K_{n}^{'} = 60 \ \mu A/V^{2} \, \pi K_{p}^{'} = 30 \ \mu A/V^{2}$

求: I<sub>DS</sub>、W、L

$$g_{\rm m} = 2\pi C_{\rm L}GBW = 1.2 \text{ mS}$$

$V_{\rm GS} - V_{\rm T} = 0.2 \text{ V}$

$$I_{DS} = g_{\rm m} \frac{V_{\rm GS} - V_{\rm T}}{2} = \frac{g_{\rm m}}{10} = 0.12 \text{ mA}$$

$$\frac{W}{L} = \frac{I_{DS}}{K'(V_{GS} - V_{T})^{2}} = 100$$

$L_{p} = L_{n} = 1 \, \mu m$  考虑增益!

$W_{\rm n}=50~\mu{\rm m}$  ,  $W_{\rm p}=100~\mu{\rm m}$

#### 目录

- 单级OTA的设计

- CMOS密勒OTA的设计

- GBW和相位裕度的设计

- 其他指标:输入范围、输出范围、SR...

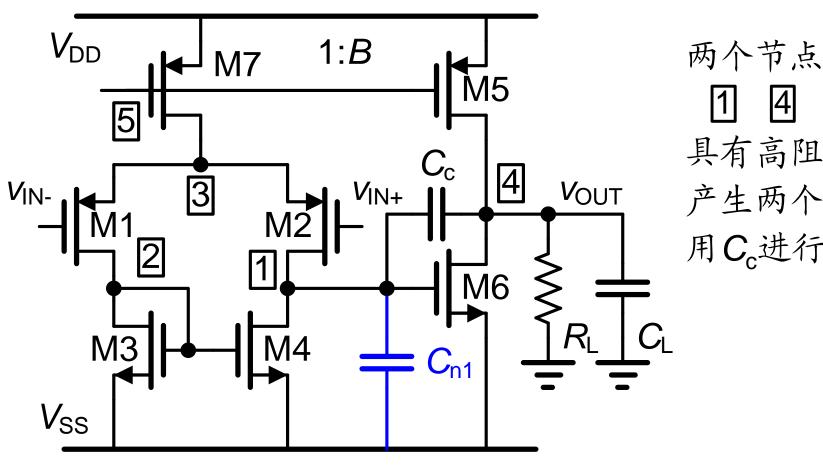

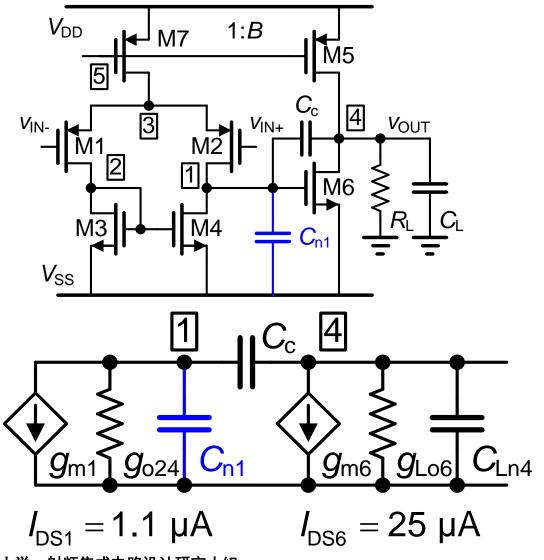

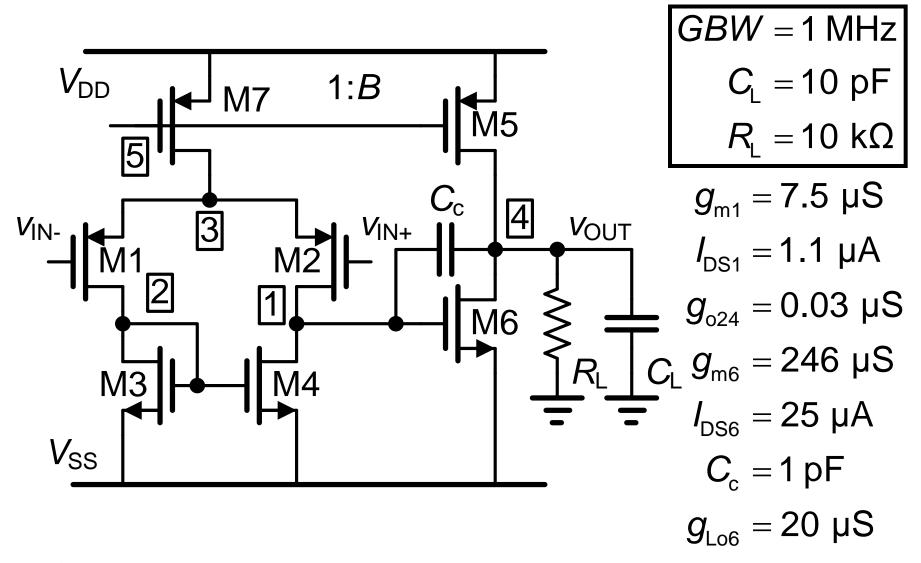

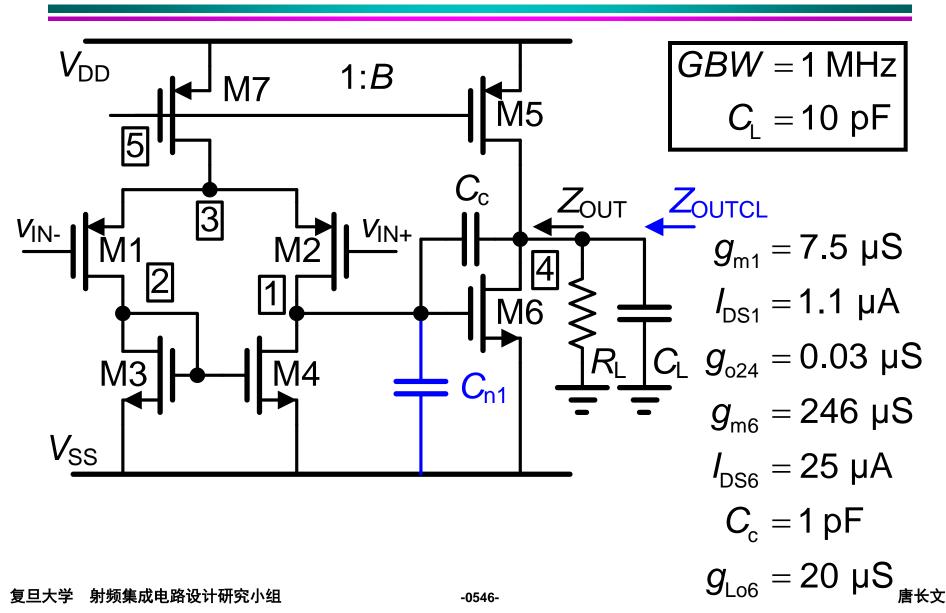

### CMOS密勒OTA

具有高阻抗 产生两个极点 用C。进行分离

### CMOS密勒OTA: 小信号

$$GBW = 1 \text{ MHz}$$

$C_L = 10 \text{ pF}$

$R_L = 10 \text{ k}\Omega$

$G_{m1} = 7.5 \text{ μS}$

$G_{o24} = 0.03 \text{ μS}$

$G_{n1} = 0.37 \text{ pF}$

$G_c = 1 \text{ pF}$

$G_{m6} = 246 \text{ μS}$

$G_{Lo6} = 20 \text{ μS}$

$G_{Lo4} = 10.2 \text{ pF}$

### CMOS密勒OTA: GBW

### CMOS密勒OTA: 极点和零点

极点分离

从

$$C_{\rm c} \approx \frac{C_{\rm n1}}{A_{\rm V2}} \approx 20 \text{ fF}$$

开始

$$C_{\rm c} = 1$$

pF足够

$$f_{z} = \frac{g_{m6}}{2\pi C_{c}}$$

#### 目录

- 单级OTA的设计

- CMOS密勒OTA的设计

- GBW和相位裕度的设计

- 其他指标:输入范围、输出范围、SR...

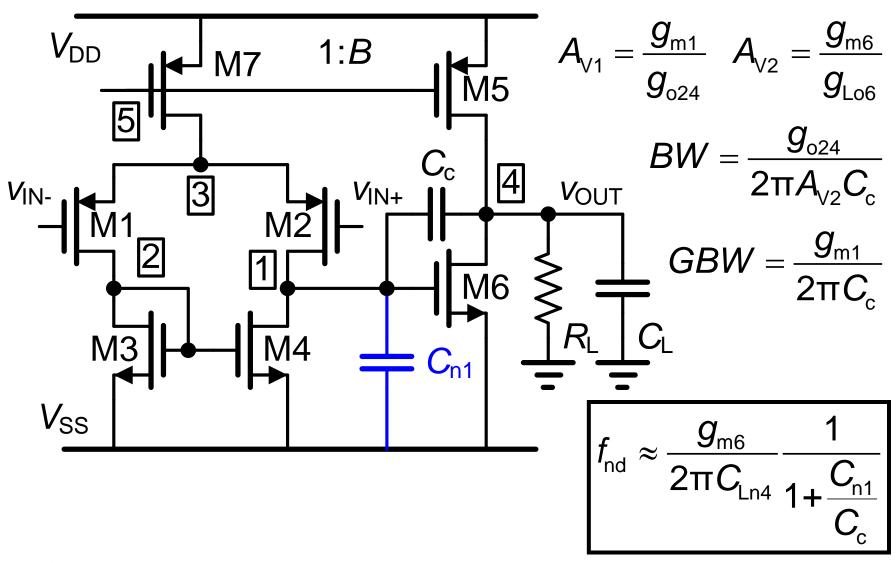

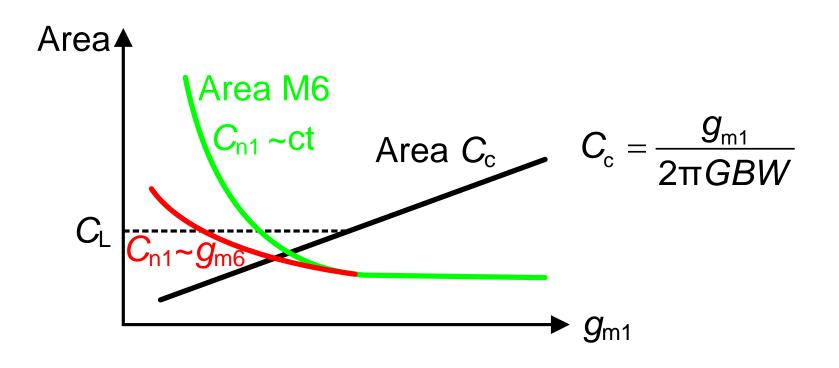

### CMOS密勒OTA: 设计规划

$$GBW = \frac{g_{\rm m1}}{2\pi C_{\rm c}}$$

$$GBW = 100 \text{ MHz}$$

$C_L = 2 \text{ pF}$

$$f_{\rm nd} \approx \frac{g_{\rm m6}}{2\pi C_{\rm Ln4}} \frac{1}{1 + \frac{C_{\rm n1}}{C_{\rm c}}}$$

两个方程,

三个变量 $g_{m1}$ 、 $g_{m6}$ 、 $C_{c}$ ?

求解:选择 $g_{m1}$ 或 $g_{m6}$ 或 $C_{c}$ ?

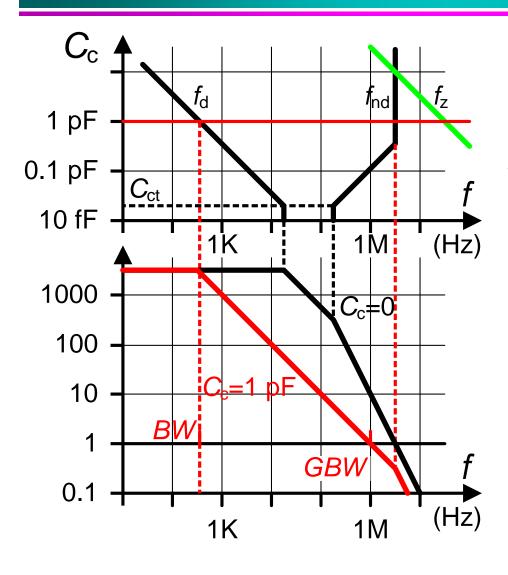

# 选择 $C_c=1$ pF 有问题吗?

# CMOS密勒OTA设计:参变量C<sub>c</sub> 1

选择

$$C_{c} \approx 3C_{n1}$$

得  $GBW = \frac{g_{m1}}{2\pi C_{c}}$  和  $3GBW \approx \frac{g_{m6}}{2\pi C_{Ln4}} \frac{1}{1.3}$

$$\frac{g_{\mathrm{m6}}}{g_{\mathrm{m1}}} pprox 4 \frac{C_{\mathrm{L}}}{C_{\mathrm{c}}}$$

$$GBW = 100 \text{ MHz}$$

$C_L = 2 \text{ pF}$

选择

$$C_{n1} < C_{c} < C_{L}$$

选择  $C_c = 1 \,\mathrm{pF}$  得  $g_{\mathrm{m}1} = 0.63 \,\mathrm{mS}$  和  $g_{\mathrm{m}6} = 5.0 \,\mathrm{mS}$

# CMOS密勒OTA设计: 参变量 $C_c$ 2

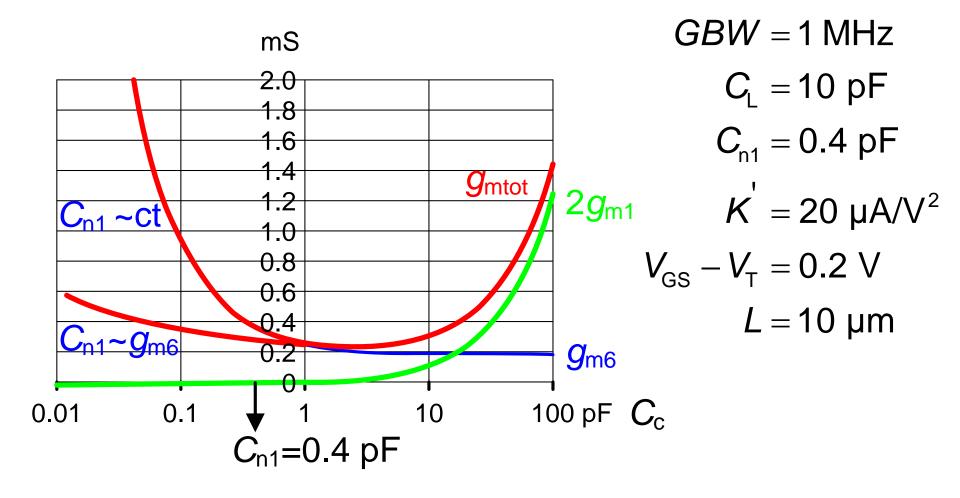

# 1 MHz CMOS密勒OTA: 参变量C<sub>c</sub>

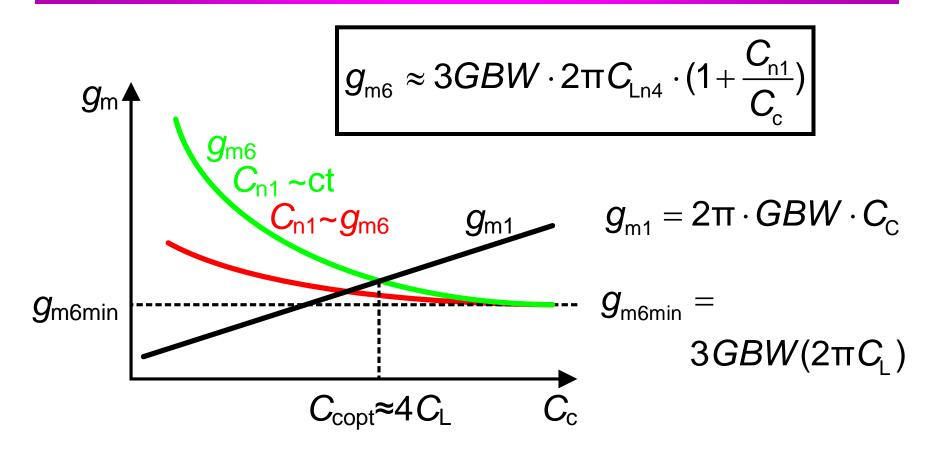

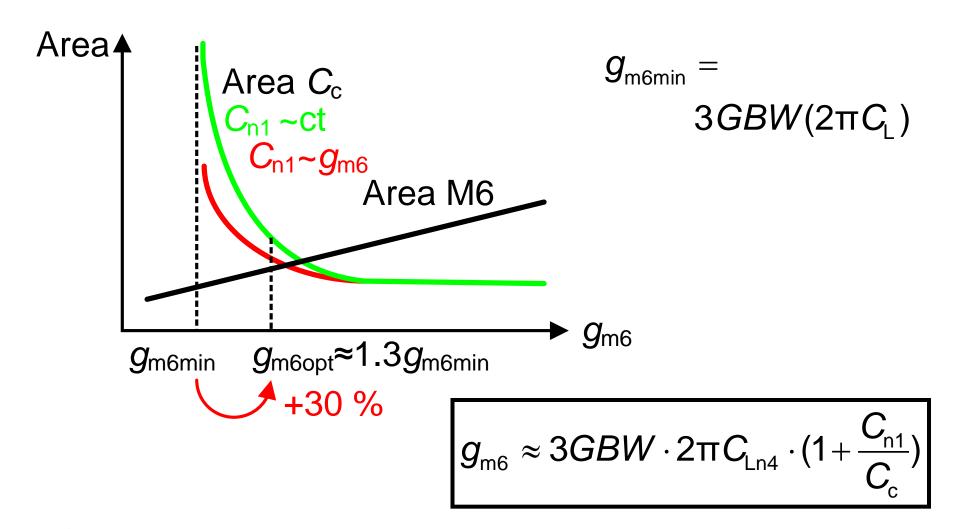

# CMOS密勒OTA设计:参变量g<sub>m6</sub>

# CMOS密勒OTA设计:参变量g<sub>m1</sub>

$$g_{\text{m6}} \approx 3GBW \cdot 2\pi C_{\text{Ln4}} \cdot (1 + \frac{C_{\text{n1}}}{g_{\text{m1}}} 2\pi GBW)$$

### 高速密勒OTA的优化设计 1

$$GBW = \frac{g_{\rm m1}}{2\pi C_{\rm c}}$$

$$f_{\rm nd} = \frac{g_{\rm m6}}{2\pi C_{\rm L}} \frac{1}{1 + C_{\rm n1}/C_{\rm c}}$$

$$C_{L} = \alpha C_{c}$$

$$\alpha \approx 2$$

$$C_{c} = \beta C_{n1} = \beta C_{GS6}$$

$\beta \approx 3$

$$f_{nd} = \gamma GBW$$

$$C_{GS} = kW$$

$$C_{GS} = kW$$

$k = 2 \text{ fF}/\mu\text{m}$

$$GBW = \frac{f_{nd}}{\gamma} = \frac{g_{m6}}{2\pi C_L} \frac{1}{\gamma (1 + 1/\beta)} = \frac{f_{T6}}{\alpha \beta \gamma (1 + 1/\beta)}$$

$$C_{L} = \alpha C_{c} = \alpha \beta C_{n1} = \alpha \beta C_{GS6} = \alpha \beta k W_{6}$$

如果C₁↑则W<sub>6</sub>↑

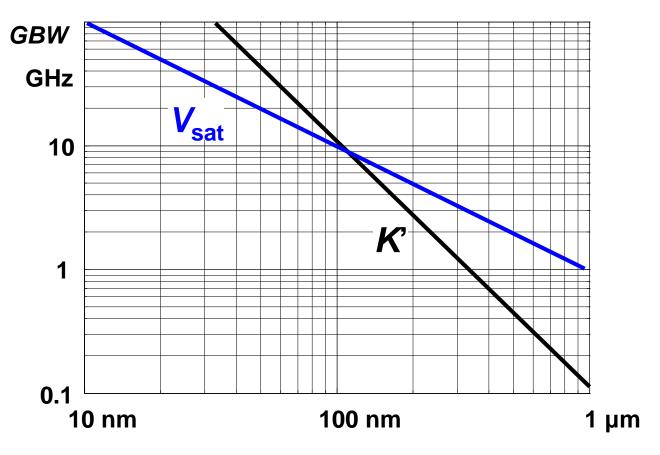

### 高速密勒OTA的优化设计 2

代入

$$f_{T6}$$

得

$$f_{T6} = rac{g_{m6}}{2\pi C_{GS6}}$$

$f_{T6} = rac{1}{L_{6min}} rac{13.5}{1 + 2.8 L_{6min} / V_{GST6}}$   $L$ 的单位为 $\mu$ m

L的单位为µm f<sub>T</sub>的单位为GHz

$$GBW = \frac{f_{T6}}{\alpha\beta\gamma(1+1/\beta)}$$

GBW不是由 $C_L$ 决定,只由 $f_T$ 决定!  $f_T$ 由L(和 $V_{GST}$ )决定!!!

当

$$V_{GST}$$

=0.2 V, $L_{min}$ <65 nm;

或 $V_{GST}=0.5 \text{ V}$ , $L_{min}<0.18 \text{ }\mu \text{m} \text{ } \text{时}$ ,晶体管进入速度饱和区

# 最大GBW与沟道长度Lmin

$$V_{GS} - V_{T} = 0.2 \text{ V}$$

$\alpha \approx 2$

$\beta \approx 3$

$\gamma \approx 2$

$16x$

$GBW \approx \frac{f_{T6}}{16}$

### 高速密勒OTA的设计优化

- 选择αβγ

- 由给定的GBW得到最小的f<sub>T6</sub>

- 由选定的(V<sub>GS6</sub>- V<sub>T</sub>)

选择最大沟道长度L<sub>6</sub>(最大化增益)

- 由CL计算W<sub>6</sub>,

确定I<sub>DS6</sub>

- 由α以及CL计算Cc

- 由Cc计算gm1和IDS1

- 由 $g_{m1}$ 或 $C_{c}$ 确定噪声

### 设计练习: GBW = 0.4 GHz & C<sub>L</sub> = 5 pF

- 选择αβγ

- 由给定的GBW得到最小的f<sub>T6</sub>

- 由选定的(V<sub>GS6</sub>- V<sub>T</sub>),

选择最大沟道长度L<sub>6</sub>(最大化增益)

- L<sub>6</sub>取最小沟道长度L<sub>min</sub>

- 由 $C_L$ 计算 $W_6$ ,确定 $I_{DS6}$  ( $K'_n = 70 \mu A/V^2$ )确定 $C_{n1}$  ( $k = 2 fF/\mu m$ )

- 由α以及CL计算Cc

- 由Cc计算gm1和IDS1

232

$$f_{T6} = 6.4 \text{ GHz}$$

- $L_6 = 0.5 \ \mu m$

- $W_{\rm e} = 417 \; \mu {\rm m}$

- $I_{DS6} = 2.3 \text{ mA}$

- $C_{n1} = 0.83 \text{ pF}$

- $C_{c} = 2.5 \text{ pF}$

- $I_{DS1} = 0.63 \text{ mA}$

### 低速密勒OTA的优化设计 1

$$GBW = \frac{f_{T6}}{\alpha\beta\gamma(1+1/\beta)}$$

$$\frac{f_{\mathsf{T}}}{f_{\mathsf{TH}}} = \sqrt{i}(1 - e^{-\sqrt{i}}) \approx \sqrt{i}(1 - 1 + \sqrt{i}) \approx i \quad \exists i \text{ ith } i \text{ the } i$$

$$f_{\rm TH} = \frac{3}{2} \frac{2\mu k T/q}{2\pi L^2}$$

GBW不是由 $C_L$ 决定,只由 $f_T$ 决定!  $f_T$ 由L和i决定!!!

### 低速密勒OTA的优化设计 2

- 选择αβγ

- 由给定的GBW得到最小的f<sub>T6</sub>

- 由给定的f<sub>TH6</sub> 选择最大沟道长度L<sub>6</sub>(最大增益)

- 计算6

- 由CL计算W<sub>6</sub>, 确定I<sub>DST6</sub>和I<sub>DS6</sub>

- 由α以及CL计算Cc

- 由Cc计算gm1和IDS1

- 由 $g_{m1}$ 或 $C_c$ 确定噪声

### 设计练习: GBW = 1 MHz & C<sub>L</sub> = 5 pF

- 选择αβγ

- 由GBW=1 MHz得到最小的f<sub>T6</sub>

- 由给定的f<sub>TH6</sub> 选择最大沟道长度L<sub>6</sub>(最大增益)

- 反型系数i

- 由 C<sub>L</sub> 计算 W<sub>6</sub>,

确定 I<sub>DST6</sub> (K'<sub>n</sub> = 70 μA/V²)

确定 I<sub>DS6</sub>

确定 C<sub>n1</sub>(k = 2 fF/μm)

- 由α以及CL计算Cc

- 由Cc计算gm1和IDS1

2 3 2

$f_{T6} = 16 \text{ MHz}$

$f_{TH6} = 2 \text{ GHz}$

$L_6 = 0.5 \ \mu m$

i = 0.008

$W_6 = 417 \; \mu \text{m}$

$I_{DST6} = 0.33 \text{ mA}$

$I_{DS6}=2.7~\mu A$

$C_{n1} = 0.83 \text{ pF}$

$C_{c} = 2.5 \text{ pF}$

$I_{DS1} = 1.6 \, \mu A$

#### 目录

- 单级OTA的设计

- CMOS密勒OTA的设计

- GBW和相位裕度的设计

- 其他指标:输入范围、输出范围、SR...

#### 1. Introductory analysis

- 1.1 DC currents and voltages on all nodes

- 1.2 Small-signal parameters of all transistors

#### 2. DC analysis

- 2.1 Common-mode input voltage range vs supply Voltage

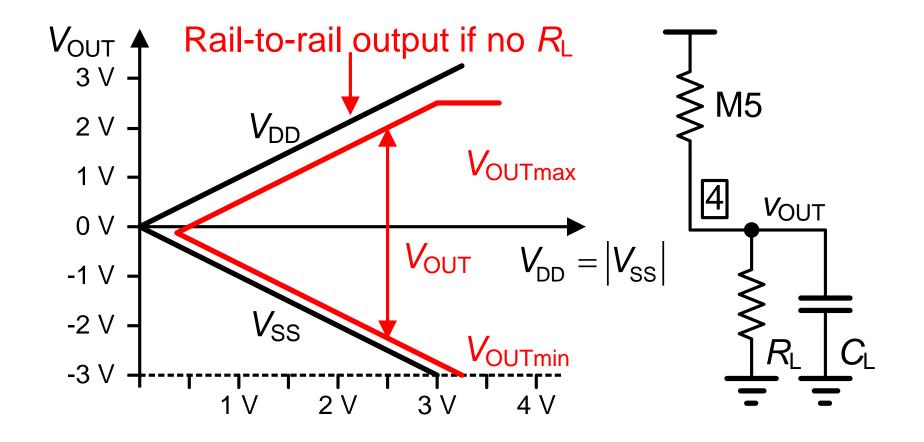

- 2.2 Output voltage range vs supply Voltage

- 2.3 Maximum output current (sink and source)

- 3. AC and transient analysis

- 3.1 AC resistance and capacitance on all nodes

- 3.2 Gain versus frequency: GBW, ...

- 3.3 Gainbandwidth versus biasing current

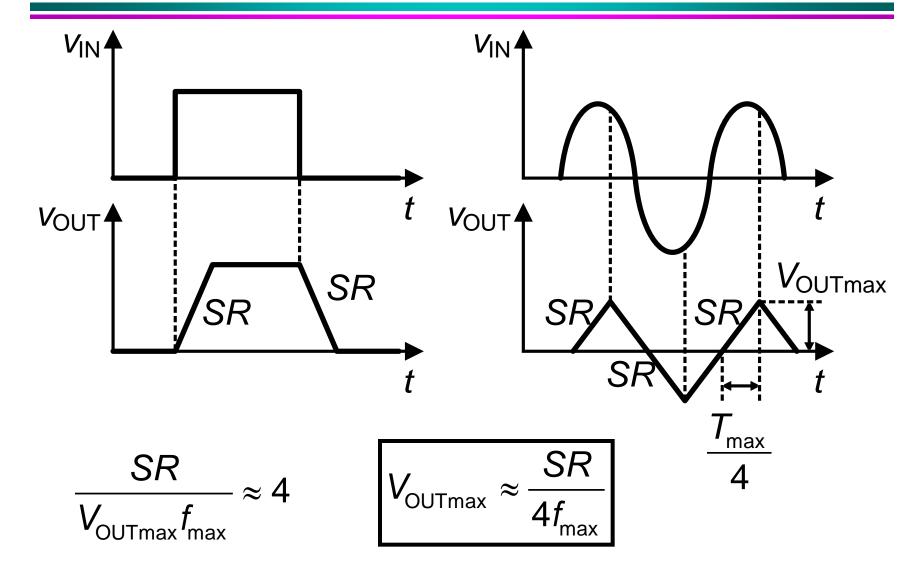

- 3.4 Slew rate versus load capacitance

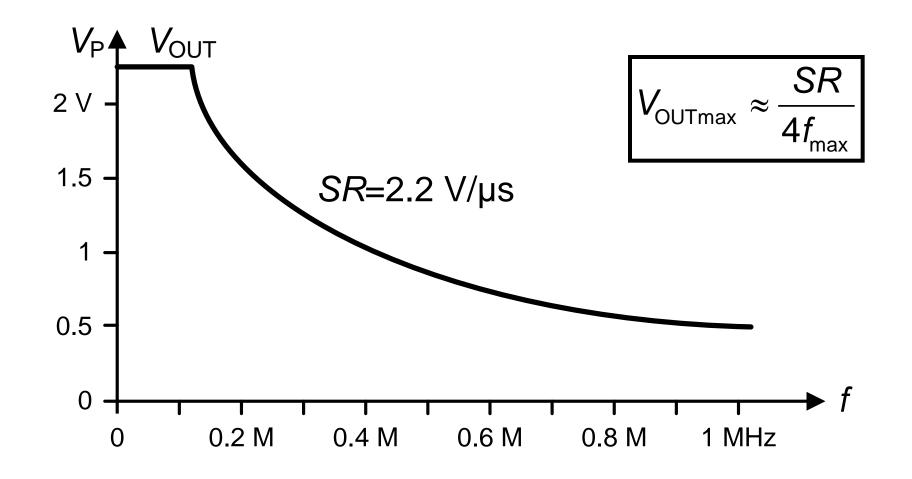

- 3.5 Output voltage range versus frequency

- 3.6 Settling time

- 3.7 Input impedance vs frequency (open & closed loop)

- 3.8 Output impedance vs frequency (open & closed loop)

- 4. Specifications related to offset and noise

- 4.1 Offset voltage versus common-mode input Voltage

- 4.2 CMRR versus frequency

- 4.3 Input bias current and offset

- 4.4 Equivalent input noise voltage versus frequency

- 4.5 Equivalent input noise current versus frequency

- 4.6 Noise optimization for capacitive/inductive sources

- 4.7 *PSRR* versus frequency

- 4.8 Distortion

- 5. Other second-order effects

- 5.1 Stability for inductive loads

- 5.2 Switching the biasing transistors

- 5.3 Switching or ramping the supply voltages

- 5.4 Different supply voltages, temperatures, ...

### MCO: 其他规范

- Common-mode input voltage range

- Output voltage range

- Slew Rate

- Output impedance

- Noise

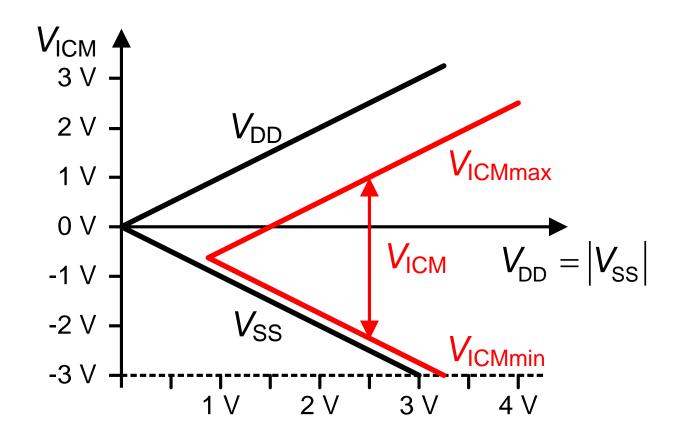

### CMOS密勒OTA

#### CMOS密勒OTA: 共模输入电压范围

#### CMOS密勒OTA: 输出电压范围

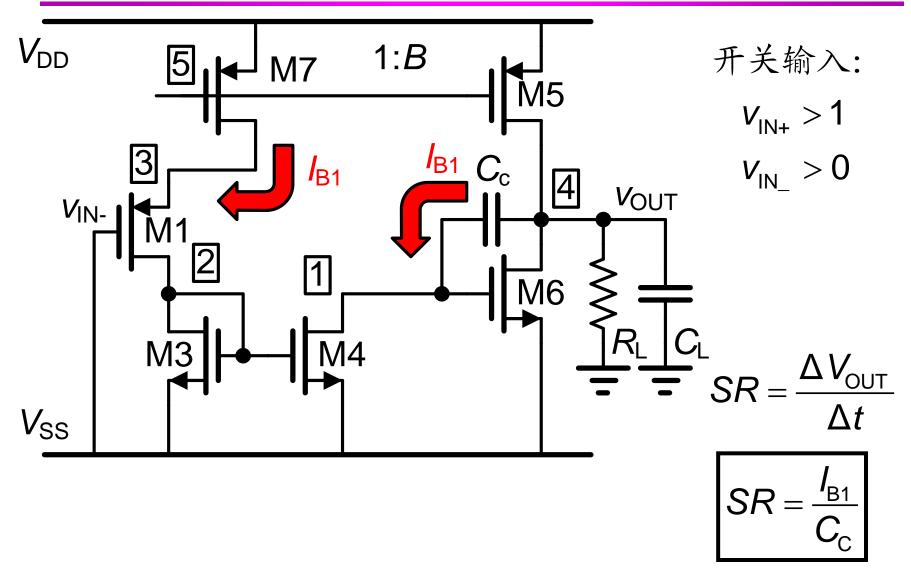

#### CMOS密勒OTA: 压摆率 1

## CMOS密勒OTA: 压摆率 2

## CMOS密勒OTA: 压摆率 3

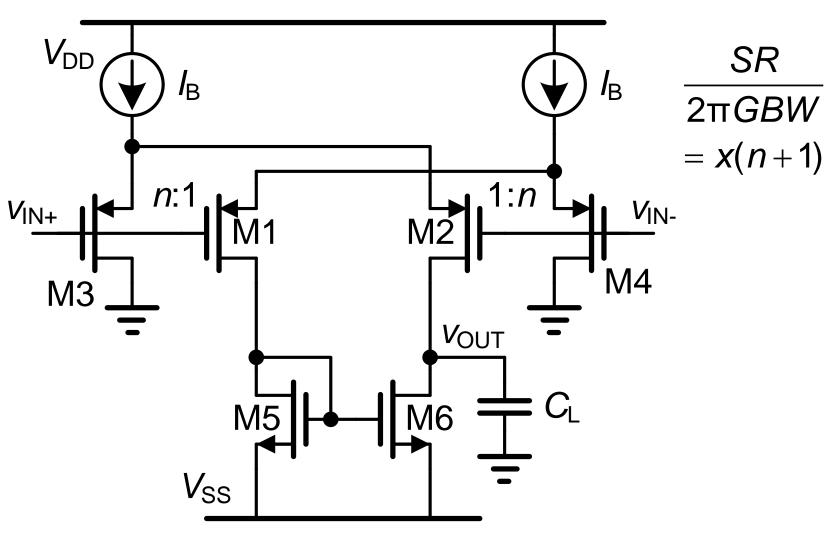

### GBW与SR的关系

$$\frac{SR}{GBW} = 4\pi \frac{I_{DS1}}{g_{m1}}$$

$\frac{I_{DS1}}{g_{m1}} = \frac{V_{GS1} - V_{T}}{2} \approx 0.1 \dots 0.3 \text{ V MOST(si)}$   $\frac{I_{DS1}}{g_{m1}} = \frac{nkT}{q} \approx 30 \dots 50 \text{ mV MOST(wi)}$   $\frac{I_{CE1}}{g_{m1}} = \frac{kT}{q} \approx 26 \text{ mV Bipolar trans.}$   $\frac{I_{CE1}}{g_{m1}} = (1 + g_{m1}R_{E})\frac{kT}{q} \approx 0.5 \text{ V }$  接 $R_{E}$

Ref.: Solomon, JSSC Dec 74, 314-332

唐长文

## 提高压摆率的方法

Ref.: Schmoock, JSSC Dec.75, 407-411

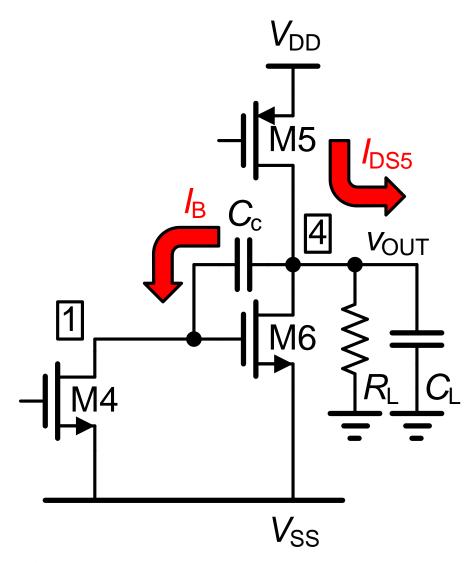

## 内部和外部压摆率

$$SR_{\text{int}} = \frac{I_{\text{B}}}{C_{\text{c}}}$$

$SR_{\text{ext}} = \frac{I_{\text{DS5}}}{C_{\text{L}}}$  比较大!

$$\frac{g_{\text{m6}}}{g_{\text{m1}}} = 4\frac{C_{\text{L}}}{C_{\text{c}}} = \frac{I_{\text{DS5}}}{I_{\text{DS1}}}$$

$$\frac{I_{\text{DS5}}}{C_{\text{L}}} \approx 2\frac{2I_{\text{DS1}}}{C_{\text{c}}}$$

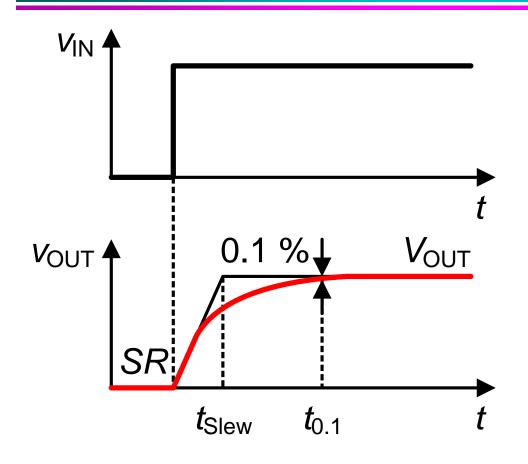

## 压摆率和建立时间

$$t_{ ext{TOT}} = t_{ ext{Slew}} + t_{0.1}$$

$t_{ ext{Slew}} = rac{V_{ ext{OUT}}}{SR}$

$t_{0.1} = rac{7}{2\pi BW}$

In(1000)  $pprox 7$

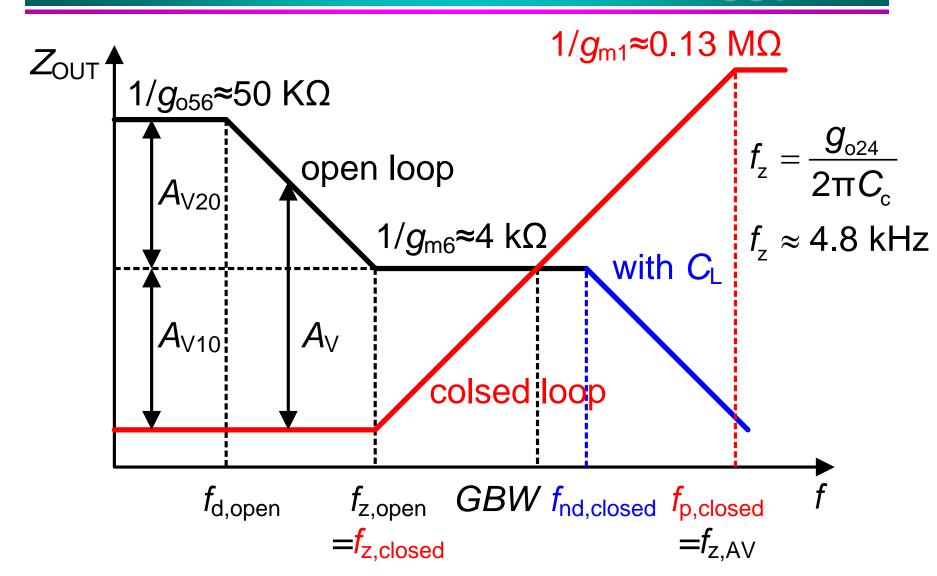

#### CMOS密勒OTA输出阻抗

# CMOS密勒OTA:输出阻抗Zout

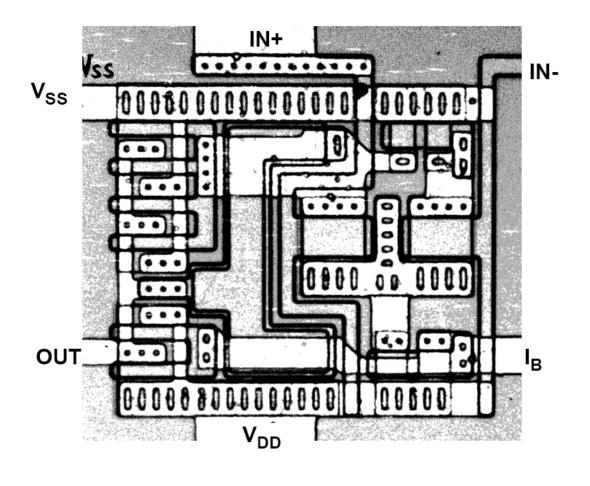

#### CMOS密勒OTA版图照片

GBW = 1 MHz  $C_L = 10 \text{ pF}$  SR = 2.2 V/µs  $V_{DD} = 5 \text{ V}$   $I_{TOT} = 27 \text{ µA}$

370 MHzpF/mA

#### 密勒CMOS OTA: 练习

已知 $GBW=50 \text{ MHz}和C_L=2 \text{ pF}:$  选用最小是 $I_{DS6}$ !

工艺参数

$$V_{GS} - V_{T} = 0.2 \text{ V}$$

求

$$g_{\text{m6}}$$

,  $I_{\text{DS6}}$ ,  $W_{\text{6}}$ ,  $C_{\text{n1}} = C_{\text{GS6}}$ ,  $C_{\text{c}}$ ,  $g_{\text{m1}}$ ,  $I_{\text{DS1}}$ ,  $dv_{\text{ineq}}^2 \not\approx v_{\text{inRMS}}$